# **Study of Real CMOS Defects**

name

matricul. nr.

group

register at: http://www.defsim.com

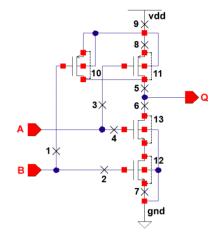

## 1. Behavior of Open Faults inside a gate

Given circuit: NA2\_o given defects:

- 1) Manually compose all possible test vectors for all given open defects in NA2\_o circuit.

- 2) Check the results in DefSim environment (http://www.defsim.com).

- 3) Fill-in the table. Analyze the behavior of defects.

| BA | Defect 1: | Defect 2: | Defect 3: |

|----|-----------|-----------|-----------|

| 00 |           |           |           |

| 01 |           |           |           |

| 10 |           |           |           |

| 11 |           |           |           |

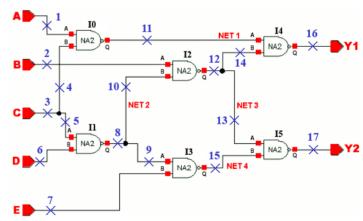

# 2. Open Faults between the gates: stuck-at-0 or stuck-at-1?

Given circuit: C17\_o given defects:

- 1) Manually compose two types of test vectors for all given open defects in *C17\_o* circuit. Find all possible test patterns for stuck-at-0 (s-a-0) and for stuck-at-1 (s-a-1) fault models.

- 2) In DefSim environment run exhaustive test for the given defect and check which ones of your vectors detect the defect.

- 3) Which fault model stuck-at-0 or stuck-at-1 does better describe the defect behavior?

| Test | Defect 1: |       | Defect 2: |       |

|------|-----------|-------|-----------|-------|

| no.  | s-a-0     | s-a-1 | s-a-0     | s-a-1 |

| 1    |           |       |           |       |

| 2    |           |       |           |       |

| 3    |           |       |           |       |

| 4    |           |       |           |       |

| 5    |           |       |           |       |

| 6    |           |       |           |       |

| 7    |           |       |           |       |

| 8    |           |       |           |       |

| 9    |           |       |           |       |

| 10   |           |       |           |       |

#### 3. Behavior of Short Defects: Wired-AND or Wired-OR?

| Given circuit: | aiven defect: |

|----------------|---------------|

| Given circuit. | given derect: |

- 1) Manually compose two types of test vectors for a given short defect in a given circuit. Find all possible test patterns for wired-AND and for Wired-OR fault models.

- 2) In DefSim environment run exhaustive test for the given defect and check which ones of your vectors detect the defect.

| No. | Wired-AND | Wired-OR |

|-----|-----------|----------|

| 1   |           |          |

| 2   |           |          |

| 3   |           |          |

| 4   |           |          |

| 5   |           |          |

| 6   |           |          |

3) Which fault model Wired-AND or Wired-OR does better describe the defect behavior?

### 4. Victim-Aggressor fault model - what is stronger input or output?

| Given circuit: | given defect: |  |

|----------------|---------------|--|

|                |               |  |

- 1) Manually find all possible test vectors for a given short between circuit's given input and output using Victim-Aggressor fault model. Consider both cases:

- a) when output is aggressor and input is victim

- b) when input is aggressor and output is victim

- 2) Apply an exhaustive test to the corresponding defective circuit and obtain the fault detection information.

- 3) Make conclusion about real victim and aggressor.

| No. | Input is stronger | Output is stronger |

|-----|-------------------|--------------------|

| 1   |                   |                    |

| 2   |                   |                    |

| 3   |                   |                    |

| 4   |                   |                    |

| 5   |                   |                    |

| 6   |                   |                    |

| 7   |                   |                    |

| 8   |                   |                    |

| 9   |                   |                    |

| 10  |                   |                    |

| 11  |                   |                    |

| 12  |                   |                    |

#### 5. Does SAF test detect all real defects in the circuit?

| $\sim$       |              |      |      |     |  |

|--------------|--------------|------|------|-----|--|

| ( -in        | /en          | cır  | CI I | ıt. |  |

| $\mathbf{v}$ | <i>,</i> – 1 | CIII | u    | IL. |  |

- 1) In DefSim, generate stuck-at fault (SAF) test for a given circuit.

- 2) Apply this test to all defects in a given circuit.

- 3) If there are undetected defects, find additional test patterns (using transistor-level schematic if necessary).

- 4) Check using DefSim, if your final test set is complete.

| Nr. | Test Patterns |

|-----|---------------|

| 1   |               |

| 2   |               |

| 3   |               |

| 4   |               |

| 5   |               |

| 6   |               |

| 7   |               |

| 8   |               |

## 6. Defect observability improvement by I<sub>DDQ</sub> measurement

Given circuit: \_\_\_\_\_

- 1) Find undetectable defects in a given circuit using exhaustive test.

- 2) Activate I<sub>DDQ</sub> and repeat the measurement. Compare the results.

- 3) Find the minimum number of test patterns needed to achieve 100% fault coverage for a given circuit. Fill them into the table.

| Nr. | Test Patterns |

|-----|---------------|

| 1   |               |

| 2   |               |

| 3   |               |

| 4   |               |

| 5   |               |