| Outline                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

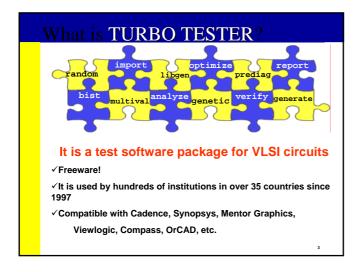

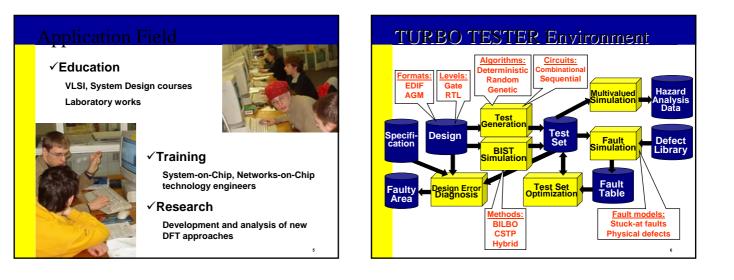

| What is TURBO TESTER?<br>TURBO TESTER Environment<br>Model Synthesis<br>Test Generation<br>BIST Simulation<br>Test Pattern Analysis<br>Test Set Optimization<br>Design Error Diagnosis<br>Live Example |

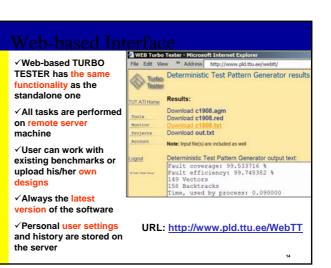

| Web-based Interface<br>Conclusion                                                                                                                                                                      |

|                                                                                                                                                                                                        |

### Built-In Self Test (BIST) approach applications:

- ✓Built-In Logic Observer (BILBO)

- ✓ Circular Self-Test Path (CSTP) ✓ Hybrid BIST

-deterministic test patterns applied after the pseudorandom ones in order to cover the hard to test faults and/or shorten the final Test Set

**Reseeding BIST (Store-and-Generate)** -the whole test sequence is generated on the basis of stored test vectors

The self-test quality of different BIST architectures can be evaluated.

A TURBO TESTER tool implies genetic search algorithm for finding good BIST architectures.

# Analysis methods:

- ✓ Fault simulation for sequential circuits

- ✓ Fault simulation for combinational circuits - Stuck-at faults

- Defect-oriented simulation uses a special defect library (includes "short-fault"; "open-fault" soon)

### ✓ Multi-valued simulation for hazard analysis

- Models possible hazards of logic circuits - 5- or 8-valued alphabets

(i.e.{"1";"0"; rising- ; falling transitions; hazards}) gate\_2: representing logic network behavior waveforms gate\_3:

- ✓The TURBO TESTER tool minimizes number of test patterns by means of static compaction

- ✓ Preprocessing step for determining the essential vectors

11

- ✓ Application of implication and Greedy search algorithm

- ✓ Fast performance (run time)

## User Documentation

TURBO TESTER installation includes a comprehensive reference manual:

- ✓The manual is constantly updated

- ✓ The documentation complies with IEEE standard Std\_1063-1987

$\checkmark$  User support is constantly available by means of Internet