# MSP430FE42x(A) ESP430CE1(A) Peripheral Module

# User's Guide

### **Chapter 1**

## **ESP430CE1(A)**

The ESP430CE1(A) module incorporates the SD16, hardware multiplier, and ESP430 embedded processor engine for use in single-phase energy metering applications. This chapter describes the ESP430CE1 and its enhancement to the ESP430CE1A. The ESP430CE1 and the ESP430CE1A modules are implemented in the MSP430FE42x and MSP430FE42xA devices, respectively.

| Topic | c P                    | age  |

|-------|------------------------|------|

| 1.1   | ESP430CE1 Introduction | 2    |

| 1.2   | ESP430CE1 Operation    | 5    |

| 1.3   | ESP430CE1 Registers    | . 57 |

|       |                        |      |

#### 1.1 ESP430CE1(A) Introduction

The ESP430CE1(A) module is designed to perform energy metering calculations independently of the CPU. The module includes the SD16 module, Hardware Multiplier module and the ESP430 embedded signal processor.

| Fea | atures of the ESP430CE1(A) include:                                                                                                  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|

|     | Complete analog and digital functionality for single-phase metering (2-wire and 3-wire applications)                                 |

|     | Tamper detection functionality                                                                                                       |

|     | Built-in calibration features and flexible user-configurable system setup                                                            |

|     | Integrated analog front end (AFE) for voltage and current sampling                                                                   |

|     | Independently configurable analog input gain and oversampling ratio                                                                  |

|     | Software selectable internal or external voltage reference                                                                           |

|     | Built-in temperature sensor                                                                                                          |

|     | Integrated processing for metering calculations including active, apparent and reactive energies, power factor, line frequency, etc. |

|     | Direct interface to hardware multiplier module                                                                                       |

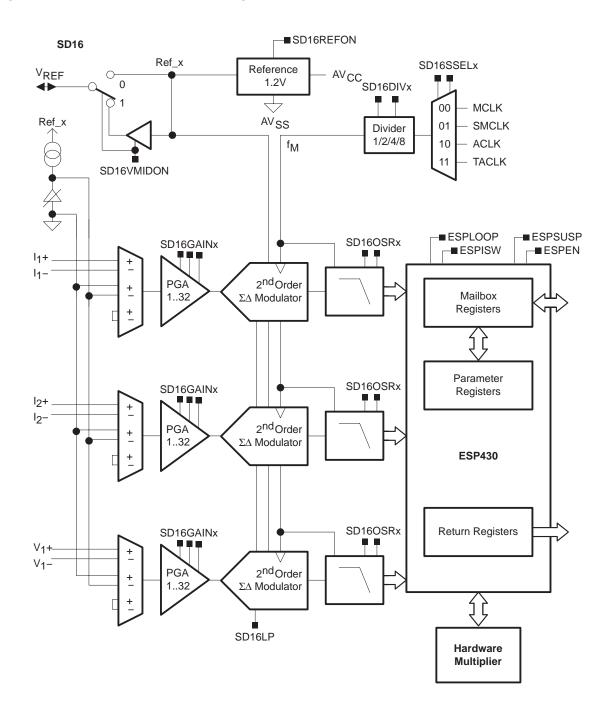

| The | e block diagram of the ESP430CE1(A) module is shown in Figure 1–1.                                                                   |

Figure 1-1. ESP430CE1(A) Block Diagram

#### 1.2 ESP430CE1(A) Operation

The ESP430CE1(A) module is configured with user software. The setup and operation of the ESP430CE1(A) is discussed in the following sections.

#### 1.2.1 ESP430 Operation and Access

The ESP430 controls the analog sampling of the module and performs the metering calculations in parallel to CPU activity. This includes dedicated access to the SD16 and hardware multiplier modules when the ESP430 is enabled. In this case, the CPU cannot control or access the SD16 or the hardware multiplier.

#### Note: Suspending the ESP430

The ESP430 can be suspended by setting ESPSUSP in ESPCTL. Once ESPSUSP = 1, a delay of 9 MCLK cycles are required prior to the CPU accessing the SD16 or hardware multiplier modules.

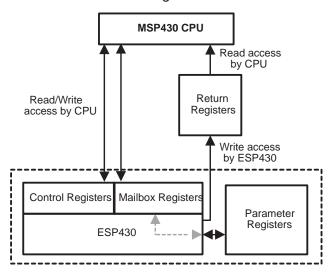

ESP430 setup, control and access is provided by accessing data and control registers. These registers fall into three categories: control and mailbox registers, parameter registers, and return registers. Figure 1–2 shows the communication links connecting each category with the ESP430 and CPU.

Figure 1-2. Module Control and Value Access Registers

The CPU controls the operation of the ESP430 which in turn controls the analog sampling and data processing of the metering analog front-end. The ESP430 also performs all parameter calculations such as active energy, apparent energy, power factor, etc. Operation of the ESP430 is performed using the ESPCTL register.

#### 1.2.2 ESP430 Modes of Operation

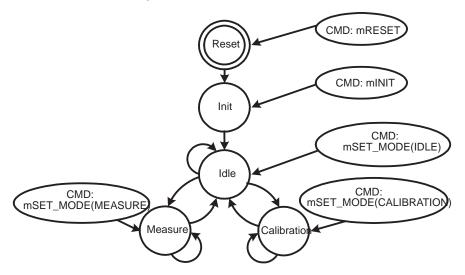

The ESP430 operating modes are shown in Figure 1–3.

Figure 1-3. ESP430 Operational State Diagram

Modes are entered through commands sent by the CPU. These commands are transmitted to the ESP430 using the mailbox communication architecture. These modes are defined in Table 1-1.

Table 1–1. ESP430 Operational Mode Summary

| Mode        | Command                    | Function                                                                                                                                                                                                                                                    |

|-------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET       | mRESET                     | ESP430CE1 module is reset:  - Parameter registers are initialized  - Return registers are cleared Upon completion, INIT mode is entered.                                                                                                                    |

| INIT        | mINIT                      | Internal offset calibration of the AFE is performed. Offset of each SD16 channel is measured and stored using the shunted ADC input. Upon completion, the IDLE mode is entered.                                                                             |

| IDLE        | mSET_MODE(IDLE)            | Operation of the ESP430 is halted. The following actions are performed in IDLE mode before halt:  - Status bits in ESP430_STAT0 are cleared  - SD16 conversions are stopped  - ESP430 data processing is stopped IDLE mode is exited by CPU-issued command. |

|             |                            | ESP430CE1: the RAM is cleared completely.                                                                                                                                                                                                                   |

|             |                            | ESP430CE1A: the RAM is cleared with the exception of the dc offset registers for I1, I2 and V1. This allows fast return to full accuracy of the ADCs.                                                                                                       |

| MEASURE     | mSET_MODE<br>(MEASURE)     | SD16 conversions active; all metering calculations are performed continuously and written to the Return registers.  IDLE mode is exited by CPU-issued command.                                                                                              |

| CALIBRATION | mSET_MODE<br>(CALIBRATION) | Calibration of analog front-end and all meter parameters active. Used during production for the purpose of calibrating meter-specific performance and constants. Upon completion, IDLE mode is entered.                                                     |

#### 1.2.3 ESP430CE1(A) Mailbox Communication

The CPU communicates with the ESP430 via the mailbox register architecture. Incoming (ESP430 to CPU) and outgoing (CPU to ESP430) mailboxes are used to control the operation of the ESP430 and for access to Parameter registers. Three groups of mailbox commands are implemented:

- Control Commands: Request defined action of the ESP430 (Outgoing)

- Parameter Commands: Modify Parameter register values (Outgoing)

- Return Commands: Acknowledge or Notification by the ESP430 (Incoming)

A total of four 16-bit registers support incoming messages (MBIN0, MBIN1) and outgoing messages (MBOUT0, MBOUT1). The use of each mailbox register is described in the following sections.

#### **Control Commands**

Mailbox control commands are sent by the CPU and define actions to be performed by the ESP430. Table 1–2 lists the available control commands.

Table 1-2. Mailbox Control Commands

| Control    |           |            | MBOUT1 Value                                      | Description                                                                                                  |  |

|------------|-----------|------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| Command    | ESP430CE1 | ESP430CE1A | <del>-</del>                                      |                                                                                                              |  |

| mRESET     | 0001h     | 0001h      | N/A                                               | ESP430 enters RESET mode. No acknowledge is returned to the CPU.                                             |  |

| mSET_MODE  | 0003h     | 0003h      | 0:IDLE                                            | ESP430 enters specified                                                                                      |  |

|            |           |            | 2:CALIBRATION                                     | mode. No acknowledge is returned                                                                             |  |

|            |           |            | 4:MEASURE                                         | to the CPU.                                                                                                  |  |

|            |           |            | 6:RESET                                           | RESET and INIT can also be                                                                                   |  |

|            |           |            | 8:INIT                                            | entered by using commands mRESET and mINIT, respectively.                                                    |  |

| mCLR_EVENT | 0005h     | 0005h      | 16-bit value specifying event flags to be cleared | Flags are cleared in ESP430_STAT0.                                                                           |  |

| mINIT      | 0007h     | 0007h      | N/A                                               | ESP430 enters INIT mode.<br>No acknowledge is returned<br>to the CPU.                                        |  |

| mTEMP      | 0009h     | 0009h      | N/A                                               | Request integrated temperature measurement. ESP430 returns mTEMPRDY in MBIN0 and conversion result in MBIN1. |  |

Table 1–2. Mailbox Control Commands (continued)

| Control MBOUT0 Value |           | MBOUT1 Value | Description                                                                                                                        |                                                                                                                                                                                                              |

|----------------------|-----------|--------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command              | ESP430CE1 | ESP430CE1A   | _                                                                                                                                  |                                                                                                                                                                                                              |

| mSWVERSION           | 000Bh     | 000Bh        | N/A                                                                                                                                | Request ESP430 firmware version. ESP430 returns mSWRDY in MBIN0 and version value in MBIN1. The ESP430 expects the CPU to accept an immediate mail return after the mSWVERSION command is issued.            |

| mREAD_PARAM          | 000Dh     | 000Dh        | Address value of parameter register to be read. See Table 1–3 for a complete list of Parameter registers and their address values. | Read Parameter register. ESP430 returns mPARAMRDY in MBIN0 and the Parameter register value in MBIN1. The ESP430 expects the CPU to accept an immediate mail return after the mREAD_PARAM command is issued. |

| ml2                  | 000Fh     | 000Fh        | N/A                                                                                                                                | Single measurement on I2 channel                                                                                                                                                                             |

| mI2_CONT             | N/A       | 0011h        | N/A                                                                                                                                | Continuous measurement on I2 channel                                                                                                                                                                         |

| mLOAD_PC             | 0011h     | 0013h        | Start address of called subroutine                                                                                                 |                                                                                                                                                                                                              |

| mSET_RES_SC          | N/A       | 0015h        | N/A                                                                                                                                | For test purposes only                                                                                                                                                                                       |

#### Note: Clearing ESP430\_STAT0 Event Flags with mCLR\_EVENT

Not all flags can be reset by the CPU due to independent activity by the ESP430. These flags include I2GTI1FG, ZXLDFG, ZXTRFG, and ACTIVEFG. See the description of the individual flags for details.

#### Temperature Measurement and the ESP430

A temperature measurement is triggered with the mTEMP command sent to the ESP430. With the next zero crossing of the signal on  $V_1$ , an internal temperature measurement is performed. Upon completion, the mTEMPRDY command is returned in MBIN0 along with the 16-bit result in MBIN1. The temperature is calculated using the equation given below.

$$T \, [^{\circ}C] = (MBIN1) \times \frac{V_{REF} \, [V] \times 1000}{65535 \times T_{C} \, [mV/K]} - \frac{V_{OFFSET} \, [mV]}{T_{C} \, [mV/K]} - 273 \, [^{\circ}C]$$

The parameters  $T_C$  and  $V_{\mbox{OFFSET}}$  refer to the temperature sensor. See the device-specific data sheet for more information.

#### **Parameter Commands**

The parameter commands are used by the CPU to access the ESP430 Parameter registers. Refer to the Parameter Register Summary section for detailed description of each Parameter register value. Table 1–3 lists each parameter command. In each instance, MBOUT1 contains the data value to be written to the specified Parameter register and is not shown.

Table 1–3. Mailbox Parameter Commands

| Parameter Command Target Register MBOUT0 Value |                |                  |

|------------------------------------------------|----------------|------------------|

|                                                | 3.5            | Register Pointer |

| mSET_CTRL0                                     | ESP430_CTRL0   | 0200h            |

| mSET_CTRL1 <sup>†</sup>                        | ESP430_CTRL1   | 0202h            |

| mSET_EVENT                                     | EVENT          | 0204h            |

| mSET_PHASECORR1                                | PHASECORR1     | 0206h            |

| mSET_PHASECORR2                                | PHASECORR2     | 0208h            |

| mSET_V1OFFSET                                  | V1OFFSET       | 020Ah            |

| mSET_I1OFFSET                                  | I1OFFSET       | 020Ch            |

| mSET_I2OFFSET                                  | I2OFFSET       | 020Eh            |

| mSET_ADAPTI1                                   | ADAPTI1        | 0210h            |

| mSET_ADAPTI2                                   | ADAPTI2        | 0212h            |

| mSET_GAINCORR1                                 | GAINCORR1      | 0214h            |

| mSET_POFFSET1_LO                               | POFFSET1_LO    | 0216h            |

| mSET_POFFSET1_HI                               | POFFSET1_HI    | 0218h            |

| mSET_GAINCORR2                                 | GAINCORR2      | 021Ah            |

| mSET_POFFSET2_LO                               | POFFSET2_LO    | 021Ch            |

| mSET_POFFSET2_HI                               | POFFSET2_HI    | 021Eh            |

| mSET_INTRPTLEVL_LO                             | INTRPTLEVL_LO  | 0220h            |

| mSET_INTRPTLEVL_HI                             | INTRPTLEVL_HI  | 0222h            |

| mSET_CALCYCLCNT                                | CALCYCLCNT     | 0224h            |

| mSET_STARTCURR_FRAC                            | STARTCURR_FRAC | 0226h            |

| mSET_STARTCURR_INT                             | STARTCURR_INT  | 0228h            |

| mSET_NOMFREQ                                   | NOMFREQ        | 022Ah            |

| mSET_VDROPCYCLS                                | VDROPCYCLS     | 022Ch            |

| mSET_RATIOTAMP                                 | RATIOTAMP      | 022Eh            |

| mSET_ITAMP                                     | ITAMP          | 0230h            |

| mSET_VDROPDLEVEL                               | VDROPDLEVEL    | 0232h            |

| mSET_VPEAKLEVEL                                | VPEAKLEVEL     | 0234h            |

| mSET_IPEAKLEVEL                                | IPEAKLEVEL     | 0236h            |

| mSET_DCREMPER                                  | DCREMPER       | 0238h            |

| mSET_DELTAV1MAX†                               | DELTAV1MAX     | 023Ah            |

| mSET_CMRRCOMP†                                 | CMRRCOMP       | 023Ch            |

| mSET_FADCU†                                    | FADCU          | 023Eh            |

<sup>&</sup>lt;sup>†</sup>A Parameter command will overwrite any existing value in the register with the new value passed in MBOUT1. The ESP430 will return the command mPARAM\_SET in MBIN0 and the requested Parameter register pointer value in MBIN1 after the register is updated. Present only in the ESP430CE1A.

#### **Return Commands**

The mailbox return commands notify the CPU that the ESP430 has completed an action or that an event has occurred. Table 1–4 lists the ESP430 return commands. Refer to the Control and Parameter Command sections for more information.

Table 1-4. Mailbox Return Commands

| Return Command | MBIN0 Value | MBIN1 Value                                                                | Description                                                                            |

|----------------|-------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| mPARAM_SET     | 0009h       | 16-bit Parameter register pointer value (see Table 1–3)                    | Acknowledge a parameter register was modified and notify CPU                           |

| mPARAMRDY      | 0007h       | 16-bit Parameter register data value                                       | Acknowledge a parameter register was queried and return value to CPU                   |

| mSWRDY         | 0005h       | ESP430 revision number                                                     | Acknowledge revision was queried and return revision number to CPU                     |

| mTEMPRDY       | 0003h       | 16-bit temperature conversion result                                       | Acknowledge a temperature measurement was requested and return result to CPU           |

| mEVENT         | 0001h       | 16-bit ESP430_STAT0 value (Refer to the ESP430_STAT0 register description) | Notify CPU that an enabled event has occurred and return ESP430_STAT0 value to the CPU |

#### 1.2.4 Sampling Rate

The AFE sampling rate is the modulator input frequency divided by the oversampling ratio:  $f_{ADC} = f_{M} / SD16OSRx$ . If not otherwise noted, the sampling rate of  $f_{ADC} = 1.048576$  MHz / 256 = 4096 Hz has been assumed.

#### **Note: SD16OSRx Settings**

The SD16OSRx settings for each SD16 channel must be identically configured for proper ESP430 operation. Failure to assign the same oversampling rate to all SD16 channels will cause erroneous ESP430 calculation results.

The number of samples for a complete ESP430 calculation sequence is 4096 and is independent of  $f_{ADC}$ . The measurement time for a complete measurement sequence is based on  $f_{ADC}$ . The sampling period is divided into 256 units to get the time base unit for the ESP430.

ESP430 timebase unit =

$$\frac{1}{f_{ADC} \times 256}$$

All timings are expressed with this unit and some common values are given in Table 1–5.

Table 1–5. ESP43 Timebase and ADC Repetition Frequencies

| f <sub>ADC</sub> | ESP430<br>Timebase Unit          | Measurement<br>Time | Minimum MCLK<br>Frequency |

|------------------|----------------------------------|---------------------|---------------------------|

| 4096 Hz          | 953.674 ns (2 <sup>-20</sup> s)  | 1.0 s               | 4.194 MHz                 |

| 2048 Hz          | 1.907348 μs (2 <sup>-19</sup> s) | 2.0 s               | 2.097 MHz                 |

| 1024 Hz          | 3.814697 μs (2 <sup>-18</sup> s) | 4.0 s               | 1.049 MHz                 |

The minimum MCLK frequency for the ESP430 is dependent upon the desired ESP430 functions to be performed and  $f_{ADC}$ . Table 1–6 shows the minimum MCLK frequency for ESP430 function combinations.

Table 1–6. Minimum MCLK Frequency (SD160SRx = 256)

| Enabled<br>Functions                                                     | Minimum<br>SD16DIVx |          | Minimum Fre<br>sampling ra |          |

|--------------------------------------------------------------------------|---------------------|----------|----------------------------|----------|

|                                                                          |                     | 1024 Hz  | 2048 Hz                    | 4096 Hz  |

| Measure I <sub>1</sub>                                                   | 10b: /4             | 2 MHz    | 4 MHz                      | 8 MHz    |

| Measure I <sub>1</sub> and I <sub>2</sub>                                | 10b: /4             | 2 MHz    | 4 MHz                      | 8 MHz    |

| Measure I <sub>1</sub> and I <sub>2</sub><br>Enable DC removal function  | 10b: /4             | 2 MHz    | 4 MHz                      | 8 MHz    |

| Measure I <sub>1</sub> and I <sub>2</sub><br>Correct for DC tolerant CTs | 11b: /8             | 2.27 MHz | 4.4 MHz                    | 8.39 MHz |

| V <sub>1</sub> filter enabled                                            |                     | 2.2 MHz  | 4.4 MHz                    | 8.39 MHz |

| All functions enabled                                                    | 11b:/8              | 2.2 MHz  | 4.4 MHz                    | 8.39 MHz |

For reduced power consumption of the ESP430CE1,  $f_{ADC}$  can be reduced. This change effects the meter-specific constants which must be modified accordingly. With a lower  $f_{ADC}$ , the MCLK frequency can be reduced with all functions remaining enabled.

#### **Note: SD16 Clock Source and Low Power Modes**

When the CPU enters low power modes, the clock source to the SD16 must not be disabled during ESP430 operation. Turning off the SD16 clock source will halt ADC conversions and ESP430 operation will halt. User software must account for this operation when low power modes are used.

#### 1.2.5 Reasons for False Measurements

The external hardware is erroneous (open and wrong connections, failures).

The MCLK frequency of the ESP430CE1(A) is too low. See previous tables for the minimum MCLK frequencies.

The ADC clock f<sub>ADC</sub> that is in use is too high for the MCLK frequency.

The measured values for V<sub>1</sub>, I<sub>1</sub>, and I<sub>2</sub> are > 7FFFh (+32767) or < 8000h (-32768). The ADC delivers the saturated values 7FFFh or 8000h. A hardware check is necessary.</li>

The values for (ADAPTI1) or (ADAPTI2) are too high. The multiplication with the ADC values for V<sub>1</sub>, I<sub>1</sub>, and I<sub>2</sub> deliver the saturated values 7FFFh or 8000h.

The V1FILTER is enabled with a too low value for (DELTAV1MAX). Too many approximated V<sub>1</sub> samples are used for the calculations.

If the ESP430CE1(A) shows false measurements, the following reasons are

#### 1.2.6 ESP430 Energy Measurement Configurations

The ESP430 can operate in two different energy measurement configurations which are summarized in Table 1–7.

Table 1–7. Measurement Configuration Summary

| Configuration                                                               | Description                                                                                                                                                              |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Energy                                                                      | Line voltage and current using V <sub>1</sub> and I <sub>1</sub> are measured. I <sub>2</sub> not used externally and is reserved for temperature                        |

| Measurement using I <sub>1</sub> only (2-wire or 3-wire meter architecture) | measurement. Limited tamper-detection capability is available:  – Disconnection of the Mains Voltage  – Reversed Meter Connections I2GTI1FG and TAMPFG always = 0        |

| Energy plus Tamper<br>Detection                                             | Line voltage and current using V <sub>1</sub> and I <sub>1</sub> are measured. I <sub>2</sub> is used to measure neutral current enabling full tamper-detect capability: |

| Measurement using I <sub>1</sub> and I <sub>2</sub> (2-wire meter           | <ul><li>Disconnection of the Mains Voltage</li><li>Reversed Meter Connections</li><li>Earthing of the Load</li></ul>                                                     |

| architecture only)                                                          | Temperature measurement is performed by $I_X$ channel and is automatically selected by the ESP430.                                                                       |

#### **Note: Tamper Detection and ADAPTx Parameter Registers**

When the energy plus tamper detect configuration is used, it is necessary to adapt the meter constants  $C_{Z1}$  and  $C_{Z2}$  using the Parameter registers ADAPT1 and ADAPT2. See the specific Parameter register descriptions for more information.

#### Disconnection of the Mains Voltage

This condition occurs when voltage connections of the electricity meter are removed. With a coil around the current path providing a supply voltage to the MSP430, basic meter functionality can continue. The CPU must sample the current channel using the SD16 directly and perform the required calculations in order to continue accumulating energy. The missing voltage value can be replaced by the highest specified mains voltage for the system. The ESP430 should be disabled to minimize current consumption.

#### Reversed Meter Connections

This condition occurs when either the voltage or the current connections of the electricity meter – but not both – are reversed. It is indicated when ACTENERGY1 contains a negative energy value. The CPU must define the treatment of negative active energy values calculated by the ESP430 and take appropriate action when negative active energy is encountered. The treatment of negative active energy by the ESP430 is defined by NE1 and NE0 in ESP430\_CTRL0 and is defined in Table 1–8.

Table 1–8. ESP430 Treatment of Negative Active Energy

| NE1 | NE0 | ESP430 Action                                                                      |

|-----|-----|------------------------------------------------------------------------------------|

| 0   | 0   | Energy not summed, active energy is set to zero, NEGENFG = 1                       |

| 0   | 1   | Absolute active energy is summed, NEGENFG = 1                                      |

| 1   | 0   | Negative active energy is summed, NEGENFG = 1 Return register POWERFCT is negative |

| 1   | 1   | Reserved                                                                           |

#### Earthing of the Load

This condition occurs when the load is not connected to the neutral return but to an earth ground connection. This is potentially the case when  $I_1$  has a significantly larger value than  $I_2$  (or vice-versa) and depends on the electricity meter circuitry. The CPU must use the provided energy values and take appropriate action.

#### Comparison of two Currents

Fundamental operation of the complete tamper detection features of the ESP430 require a comparison of currents on both  $I_1$  and  $I_2$ . The ESP430 measures the meter current at  $I_1$  and  $I_2$  when both channels are used and the larger of the two RMS values is used for all calculations.

I2GTI1FG in Return register ESP430\_STAT0 indicates the channel measuring the greater current:

```

– I2GTI1FG = 0: I_1 ≥ I_2. Current I1 is used

```

- I2GTI1FG = 1:  $I_1 < I_2$ . Current I2 is used

TAMPFG in Return register ESP430\_STAT0 indicates if tampering (defined by Parameter register RATIOTAMP) occurred during the last measurement period (4096 samples). RATIOTAMP defines the percentage difference between both  $I_X$  channels allowed before a possible tampering condition is indicated (0% to 100%:  $1.0 \le \langle RATIOTAMP \rangle \times 2^{-14} < 2.0$ ).

TAMPFG = 0: no tampering detected

- I2GTI1FG = 0:  $I_1 < I_2 \times \langle RATIOTAMP \rangle \times 2^{-14}$

- I2GTI1FG = 1:  $I_2 < I_1 \times (RATIOTAMP) \times 2^{-14}$

TAMPFG = 1: possible tampering condition

- I2GTI1FG = 0:  $I_1 \ge I_2 \times \langle RATIOTAMP \rangle \times 2^{-14}$

- I2GTI1FG = 1:  $I_2 \ge I_1 \times \langle RATIOTAMP \rangle \times 2^{-14}$

The tampering check threshold for each channel is defined by the ITAMP Parameter register. If the RMS values of  $I_1$  and  $I_2$  are lower than the tamper threshold current provided, the tamper check calculations are not performed and TAMPFG = 0.

#### 1.2.7 Meter Constants and the ESP430

The ESP430 processes AFE conversion data and calculates the Return register results. With user software, the CPU calculates meter-specific values for voltage, current, energy, power, etc. from the relative values provided by the ESP430. In order to calculate the meter-specific values from the relative values provided by the ESP430, meter constants must be defined.

The meter constant  $C_Z$  is given by:

$$C_{z} = \frac{f_{ADC}}{k_{v} \times k_{l} \times 4096} \left[ \frac{steps^{2}}{Ws} \right]$$

When  $f_{ADC} = 4096Hz$  this simplifies to:

$$C_Z = \frac{1}{k_V \times k_I \times 1sec} \left[ \frac{steps^2}{Ws} \right]$$

The variables  $k_V$  and  $k_I$  represent the meter-specific constants used by the CPU to calculate actual voltages and currents from the values of the Return registers. Different constants can exist for each current path and are differentiated by a 1 or 2 for  $I_1$  and  $I_2$ , respectively, where appropriate. Return value equations used by the ESP430 and meter-specific relationships used by the CPU are described in the following sections.

#### Note: Equations and ESP430 Registers

Throughout this document, equation variables enclosed in "()" refer to values contained in ESP430 Parameter or Return registers.

#### 1.2.8 ESP430CE1 Parameter Register Description

The Parameter registers contain information provided by the CPU that controls how the ESP430 processes the current and voltage sample data.

The Parameter registers are located within the ESP430 and are accessed using the mailbox communication registers. The following section describes each Parameter register.

#### ESP430\_CTRL0: ESP430 Control Register 0

The ESP430\_CTRL0 register controls the calculation functionality of the ESP430 and is described in Table 1–9.

Table 1-9. ESP430\_CTRL0 Summary

| Name       | Bit Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CURR_I2    | CURR_I2 enables the external use of analog channel I <sub>2</sub> .  - CURR_I2 = 0: I <sub>2</sub> is disabled and not used externally  - CURR_I2 = 1: I <sub>2</sub> accepts a connection to a current transformer (CT), DC-tolerant CT or shunt sensor for tamper detection operation.                                                                                                                                                                                                                                                                          |

| CURR_I1    | CURR_I1 enables the external use of analog channel I <sub>1</sub> .  – CURR_I1 = 0, I <sub>1</sub> accepts a connection to a CT, DC-tolerant CT or shunt sensor for measurement of the line current  – CURR_I1 = 1: Reserved                                                                                                                                                                                                                                                                                                                                      |

| МВ         | MB defines the operation ILREACHEDFG indicating that an interrupt level has been reached specified in the INTRPTLEVL Parameter register.  – MB = 0: ILREACHEDFG is set after a defined accumulated energy level has been reached specified by INTRPTLEVL. The value in INTRPTLEVL is subtracted from the ESP430 energy sum and accumulation of energy continues.  – MB = 1: ILREACHEDFG is set after a defined number of measurements has been completed specified by INTRPTLEVL. The ESP430 internal measurement counter is cleared and counting resumes from 0. |

| NE0<br>NE1 | NEx bits define the ESP430 handling of a negative active energy result. Refer to Table 1–8 for additional information.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DCREM_V1   | DCREM_xx enables the ESP430 DC removal functionality for measurements made on the respective AFE channel: V <sub>1</sub> , I <sub>1</sub> , or I <sub>2</sub> .                                                                                                                                                                                                                                                                                                                                                                                                   |

| DCREM_I1   | <ul> <li>DCREM_xx = 0: the removal function is disabled. ADC conversion values are corrected using the offset correction value obtained for the specific AFE channel during the INIT mode of the ESP430 startup operation.</li> </ul>                                                                                                                                                                                                                                                                                                                             |

| DCREM_I2   | <ul> <li>DCREM_xx = 1: the removal function is enabled. ADC conversion values are corrected using the DC removal function.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V1FILTER   | The V1FILTER Bit (bit 8) switches the spike filter function for the voltage V1. Implemented with the ESP430CE1A only.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| I2CMRR     | The CMRR Enable Bit (bit 9) switches the common mode rejection function for the current I2. Implemented with the ESP430CE1A only.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### Note: Enabling DC Removal for Multiple AFE Channels

It is not necessary to enable DC removal for all channels, and it must be enabled only for the voltage path or the current path. When both  $I_1$  and  $I_2$  are used, and DC removal is required in the current path, the DC removal function can be enabled for both current channels as required by the measurement configuration.

#### DC Removal Bit for V<sub>1</sub> – DCREM\_V1

The DCREM\_V1 Bit (bit 5) switches the dc removal function for the voltage V1. A description of the dc removal is given in section "DC Removal Period Count".

#### **ESP430CE1**

DCREM\_V1 = 0: The dc removal function for  $V_1$  is switched off, the ADC offset  $N_{V1SC}$  measured with shorted ADC inputs for V1 is used instead.

DCREM\_V1 = 1: The dc removal function for  $V_1$  is switched on.

#### ESP430CE1A

DCREM\_V1 = 0: The dc removal function for  $V_1$  is switched off, an ADC offset 0 is used instead.

DCREM\_V1 = 1: The dc removal function for  $V_1$  is switched on.

#### DC Removal Bit for I1 - DCREM\_I1

The DCREM\_I1 Bit (bit 6) switches the dc removal function for the current I<sub>1</sub>.

#### **ESP430CE1**

DCREM\_I1 = 0: The dc removal function for  $I_1$  is switched off, the ADC offset  $N_{I1SC}$  measured with shorted ADC inputs for  $I_1$  is used instead.

DCREM\_I1 = 1: The dc removal function for  $I_1$  is switched on. If a Rogowski coil is used (CURR\_I1 = 1) the dc removal for the di/dt integrator is enabled, too.

#### ESP430CE1A

DCREM\_I1 = 0: The dc removal function for  $I_1$  is switched off, an ADC offset 0 is used instead.

DCREM\_I1 = 1: The dc removal function for  $I_1$  is switched on.

#### DC Removal Bit for I2 - DCREM I2

The DCREM\_I2 Bit (bit 7) switches the dc removal function for the current I2.

#### **ESP430CE1**

DCREM\_I2 = 0: The dc removal function for  $I_2$  is switched off, the ADC

offset N<sub>I2SC</sub> measured with shorted ADC inputs for I<sub>2</sub> is

used instead.

DCREM\_I2 = 1: The dc removal function for  $I_2$  is switched on.

ESP430CE1A

DCREM\_I2 = 0: The dc removal function for  $I_2$  is switched off, an ADC

offset 0 is used instead.

DCREM\_I2 = 1: The dc removal function for  $I_2$  is switched on.

#### Spike Filter Enable Bit for $V_1$ – V1FILTER

The V1FILTER Bit (bit 8) switches the spike filter function for the voltage V1. Implemented with the ESP430CE1A only.

V1FILTER = 0: No filter function. The  $V_1$  input samples are not checked.

V1FILTER = 1: The spike filter function for  $V_1$  is enabled. The absolute

value of the difference  $|N_{V1n} - N_{V1n-1}|$  is compared to the value contained in word DELTAV1MAX. If the absolute value of this difference is smaller, the original  $V_1$  sample is used. If the difference is larger or equal, a linear approximation of the two previous  $V_1$  values  $(N_{V1n-1}, N_{V1n-2})$  is used instead for  $N_{V1n}$ . See section

"Maximum Spike for V<sub>1</sub> Filter" for details.

#### CMRR Enable Bit for I<sub>2</sub> – I2CMRR

The CMRR Enable Bit (bit 9) switches the common mode rejection function for the current I<sub>2</sub>. Implemented with the ESP430CE1A only.

I2CMRR = 0: No common-mode rejection function for  $I_2$ . This allows

the use of current sensors with relatively high output

voltages like current transformers.

I2CMRR = 1: The common-mode rejection function for  $I_2$  is enabled, if

the value in parameter register CMRRCOMP > 0. See section "Common Mode Rejection Ratio" for details.

#### **EVENT: Event Message Enable Control Register**

The message enable bits in EVENT enable a mEVENT mailbox message return command to be sent by the ESP430 to the CPU when the corresponding event occurs. An event is the setting of a previously cleared bit in the ESP430\_STAT0 register. A static level of a flag in ESP430\_STAT0 or resetting of a flag not previously cleared will not generate an event. The event flags in ESP430\_STAT0 are set independently of the message enable settings.

#### PHASECORRx: I<sub>x</sub> Phase Correction

PHASECORRx defines the phase correction for  $I_x$  where x=1 or 2 for channels  $I_1$  and  $I_2$ , respectively. The value specified is used for phase error correction of a simple or DC tolerant current transformer on  $I_x$ . If this value is non–zero, the correction calculations are made during the measurement process. If a shunt is used on  $I_x$ , set PHASECORRx = 0.

PHASECORRx > 0:  $I_X$  leads  $V_1$  (capacitive characteristic of DC tolerant CTs) PHASECORRx < 0:  $I_X$  lags  $V_1$  (inductive characteristic of simple CTs)

| Format         | Signed integer                                                                            | ±15.0                                                                                 |

|----------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Range          | 0x8000 to 0x7FFF                                                                          | -31.25 ms to +31.2490 ms<br>(f <sub>MAINS</sub> = 50Hz,<br>f <sub>ADC</sub> = 4096Hz) |

| Normal Range   | -2° to +8°: 0xFF8C to 0x01D2<br>(f <sub>MAINS</sub> = 50Hz,<br>f <sub>ADC</sub> = 4096Hz) | -111 us to +444 us<br>(f <sub>MAINS</sub> = 50Hz,<br>f <sub>ADC</sub> = 4096Hz)       |

| Resolution     | ESP430 timebase unit                                                                      | $2^{-20}$ s (f <sub>ADC</sub> = 4096Hz)                                               |

| Initialization | 0x00                                                                                      |                                                                                       |

Formulas:

$$(\text{PHASECORRx}) = \frac{\phi_{\text{CT}}}{360^{\text{o}} \text{ x f}_{\text{MAINS(nom)}}} \text{ x } \frac{1}{\text{ESP430 Timbase Unit}}$$

Example: The phase error,  $\phi_{CT}$ , of a DC tolerant current transformer on I<sub>1</sub> is specified to be +4.2° at 50 Hz; f<sub>ADC</sub> = 4096 Hz. The rounded value calculated for PHASECORR1 is:

(PHASECORR1) =

$$\frac{4.2^{\circ}}{360^{\circ} \text{ x } 50\text{Hz}} \text{ x } \frac{1}{2^{-20}} = 244.667 \approx 0\text{x}5\text{F}$$

Example: A simple current transformer on  $I_1$  has an inductive phase error of  $-1^{\circ}$  at 50 Hz;  $f_{ADC} = 4096$  Hz. The rounded value in PHASECORR1 is:

(PHASECORR1) =

$$\frac{-1.0^{\circ}}{360^{\circ} \text{ x } 50 \text{Hz}} \text{ x } \frac{1}{2^{-20}} = -58.254 \approx 0 \text{xFFC6}$$

#### V10FFSET: V<sub>1</sub> Offset Correction

V1OFFSET defines the ADC offset correction for V<sub>1</sub>. The value specified is added to the ADC result in order to measure 0 when 0V is applied externally.

| Format         | Signed integer   | ±15.0              |

|----------------|------------------|--------------------|

| Range          | 0x8000 to 0x7FFF | -32,768 to +32,767 |

| Normal Range   | 0xFE00 to 0x0200 | ±512               |

| Resolution     | 1 step           |                    |

| Initialization | 0x00             |                    |

Formulas:

$$(WAVEFSV1) = N_{V1ADC} - N_{V1SC} + (V1OFFSET)$$

Where:

N<sub>V1ADC</sub>: Conversion value from SD16 N<sub>V1SC</sub>: ESP430-corrected offset value

$N_{V1SC}$  represents two different values dependent on DCREM\_V1:

DCREM\_V1 = 0:  $N_{V1SC}$  is the offset measured during the INIT mode of the ESP430 startup (internally shorted ADC input result)

DCREM\_V1 = 1:  $N_{V1SC}$  is the offset resulting from the ESP430 DC removal calculation for  $V_1$ . V1OFFSET is not used and should be set to 0.

#### IxOFFSET: IX Offset Correction

IxOFFSET defines the ADC offset correction for  $I_X$  where x=1 or 2 for channels  $I_1$  and  $I_2$ , respectively. The value specified is added to the ADC result in order to measure when 0A is applied to the shunt or CT externally for the respective  $I_X$  channel.

| Format         | Signed integer   | ±15.0              |

|----------------|------------------|--------------------|

| Range          | 0x8000 to 0x7FFF | -32,768 to +32,767 |

| Normal Range   | 0xFE00 to 0x0200 | ±512               |

| Resolution     | 1 step           |                    |

| Initialization | 0x00             |                    |

Formulas:

(WAVEFSIx) =

$$(N_{IXADC} - N_{IXSC} + (IxOFFSET)) x (ADAPTIx) x 2^{-14}$$

Where:

N<sub>IxADC</sub>: Conversion value from SD16 N<sub>IxSC</sub>: ESP430-corrected offset value

N<sub>IxSC</sub> represents two different values dependent on DCREM\_Ix:

DCREM\_Ix = 0:  $N_{IxSC}$  is the offset measured during the INIT mode of the ESP430 startup (internally shorted ADC input result)

DCREM\_Ix = 1:  $N_{IxSC}$  is the offset resulting from the ESP430 DC removal calculation for  $I_x$ . IxOFFSET is not used and should be set to 0.

#### **ADAPTIX: Ix Adaptation Current**

ADAPTIx defines the multiplication factor for the adaptation of the  $I_{x}$  ADC result. This parameter is used to provide equal current constants  $k_{l1}$  and  $k_{l2}$  (and therefore equal meter constants  $C_{Z1}$  and  $C_{Z2}$ ) for the currents  $I_{1}$  and  $I_{2}$  despite possible hardware implementation differences. In order to assure that the meter constants can be adapted,  $I_{1}$  and  $I_{2}$  should be matched as close as possible using the AFE gain settings.

| Format         | unsigned Integer.Fraction | +1.14              |

|----------------|---------------------------|--------------------|

| Range          | 0x00 to 0x7FFF            | 0.0 to 1.999938965 |

| Normal Range   | 0x2000 to 0x7FFF          | 0.5 to 1.999938965 |

| Resolution     | 61.035x10 <sup>-6</sup>   | 2-14               |

| Initialization | 0x4000                    | 1.000              |

Formulas:

$$(ADAPTIx) = \frac{k_{lx}}{k_{lcom}} \times 2^{14}$$

Where:

k<sub>lx</sub>: I<sub>x</sub> meter constant

k<sub>Icom</sub>: Common meter constant

Example: The I<sub>1</sub> meter constant should be modified to  $k_{lcom} = 2.5 \times 10^{-3}$  from the actual meter constant  $k_{l1} = 2.21946 \times 10^{-3}$ . The rounded value required in ADAPTI1 is:

(ADAPTI1) =

$$\frac{k_{l1}}{k_{lcom}} \times 2^{14} = \frac{2.21946 \times 10^{-3}}{2.5 \times 10^{-3}} \times 2^{14} = 0.887784 \times 2^{14} =$$

= 14,545.45306  $\approx 0 \times 38D1$

#### **Note: ADAPTIx Minimum Values**

The I<sub>1</sub> ADC result WAVEFSI1 is corrected with the offset correction value I1OFFSET, the offset value N<sub>I1SC</sub> which depends on DCREM\_I1 and the value in ADAPTI1. It is recommended that ADAPT1\*2<sup>-14</sup>  $\geq$  1. Results less than 1 may degrade calculation accuracy. This also applies to ADAPTI2.

#### GAINCORRx: Ix Gain Correction

GAINCORRx defines the slope for the correction of the product WAVEFSV1\*WAVEFSIx, where x = 1 or 2 for channels  $I_1$  and  $I_2$ , respectively. Before internally summing the new value, the product of the new voltage and current samples is corrected with GAINCORRx and POFFSETx. Refer to "ESP430CE1A Calibration" for more information.

| Format         | unsigned Integer.Fraction | +1.14              |

|----------------|---------------------------|--------------------|

| Range          | 0x00 to 0x7FFF            | 0.0 to 1.999938965 |

| Normal Range   | 0x3999 to 0x4666          | 1±10%              |

| Resolution     | 61.035x10 <sup>-6</sup>   | 2-14               |

| Initialization | 0x4000                    | 1.000              |

#### Formulas:

$$(\text{GAINCORRx}) \, = \, \text{slope x} \, \, 2^{\text{14}} \, = \, \frac{n_{\text{HIcalc}} \, - \, n_{\text{LOcalc}}}{n_{\text{HImeas}} \, - \, n_{\text{LOmeas}}} \, \, \text{x} \, \, 2^{\text{14}}$$

Where:

$n_{Hlcalc}$ : Calculated result at the high current calibration point <code>[steps2]</code>  $n_{Hlmeas}$ : Measured result at the high current calibration point <code>[steps2]</code>  $n_{LOcalc}$ : Calculated result at the low current calibration point <code>[steps2]</code>  $n_{LOmeas}$ : Measured result at the low current calibration point <code>[steps2]</code>

n<sub>LOcalc</sub> and n<sub>LOmeas</sub> are both zero for a single point calibration.

Example: Calibration resulted in a necessary gain correction of 1.0145 (slope). The value in GAINCORR1 is:

$$(GAINCORR1) = 1.0145 \times 2^{14} = 16,621.568 \approx 0x40EE$$

#### POFFSETx: Ix Power Offset Correction

POFFSETx (POFFSETx = POFFSETx\_HI,POFFSETx\_LO = 32-bit value) defines the offset for the correction of the product WAVEFSV1\*WAVEFSIx, where x = 1 or 2 for channels  $I_1$  and  $I_2$ , respectively. Before internally summing the new value, the product of the new voltage and current samples is corrected with GAINCORRx and POFFSETx. Refer to "ESP430CE1A Calibration" for more information.

| Format       | Signed integer             | ±31.0                      |

|--------------|----------------------------|----------------------------|

| Range        | 0x8000,0000 to 0x7FFF,FFFF | -2.14748E+9 to +2.14748E+9 |

| Normal Range | 0xFF00,0000 to 0x100,0000  | ±2 <sup>24</sup>           |

| Resolution   | 1 step <sup>2</sup>        |                            |

#### Formulas:

$$\mathsf{P}_{\mathsf{lx}} = \frac{(\mathsf{WAVEFSIx}) \: \mathsf{x} \: (\mathsf{WAVEFSV1}) \: \mathsf{x} \: (\mathsf{GAINCORRx})}{2^{\mathsf{14}}} + (\mathsf{POFFSETx})$$

Where:

$P_{IX}$ : Corrected internal ESP430 power calculation for channel  $I_X$

#### **Note: POFFSETx Value Format**

POFFSETx values are expressed in the internal number format used by the ESP430. These values are 4096 times larger than the calculated energy contained in addresses ACTENERGY1 and ACTENERGY2. This is due to the adaptation of the energy to the meter constants  $C_{Z1}$  and  $C_{Z2}$ .

#### **INTRPTLEVL: Energy Overflow Interrupt Level**

INTRPTLEVL (INTRPTLEVL = INTRPTLEVL\_HI, INTRPTLEVL\_LO = 32-bits) defines the trigger threshold for setting ILREACHEDFG in ESP430\_STAT0. MB controls how the ESP430 uses INTRPTLEVL.

**MB = 0**: ILREACHEDFG = 1 when the ESP430 accumulated energy count reaches the value in INTRPTLEVL. INTRPTLEVL is subtracted from the ESP430 accumulated energy count and accumulation resumes. ILREACHEDFG is set with the repetition frequency  $f_{\parallel L}$ .

**MB = 1**: ILREACHEDFG = 1 when the number of ESP430 measurement cycles performed reaches the value in INTRPLEVL. The 32-bit measurement count contained in NMBMEAS is cleared and measurement counting restarts at 0.

| Format         | Unsigned integer                                     | +32.0             |

|----------------|------------------------------------------------------|-------------------|

| Range          | 0x00 to 0x0FFFF,FFFF                                 | 0 to +4.294967E+9 |

| Resolution     | MB = 0: 1 step <sup>2</sup><br>MB = 1: 1 measurement |                   |

| Initialization | 0x8000,0000                                          | 2.147483E+9       |

Formulas:

Interrupt level frequency:

$$\begin{split} f_{\text{IL}} &= \text{P [W] x Interrupt Rate } [1/\text{Ws}] = \frac{\text{P x 4096 x C}_{\text{Z}}}{(\text{INTRPTLEVL})} \\ \text{Energy per pulse } [\text{Ws}] &= \frac{1}{\text{Interrupt Rate}} = \frac{(\text{INTRPTLEVL})}{4096 \text{ x C}_{\text{Z}}} \\ f_{\text{IL(min)}} &= \frac{\text{P x 4096 x C}_{\text{Z}}}{0\text{xFFFF, FFFF}} \\ f_{\text{IL(max)}} &= f_{\text{ADC}} \rightarrow (\text{INTRPTLEVL})_{\text{min}} > \frac{P_{\text{max}} \text{ x 4096 x C}_{\text{Z}}}{f_{\text{ADC}}} \\ \text{Error}_{\text{fIL(max)}} &= \frac{1}{(\text{INTRPTLEVL})_{\text{min}}} = \frac{f_{\text{ADC}}}{P_{\text{max}} \text{ x 4096 x C}_{\text{Z}}} \end{split}$$

Example: ILREACHEDFG is to be set with a mean repetition frequency of  $f_{IL}$  = 2kHz for a power P = 3kW. The  $I_1$  meter constant of the meter is  $C_{Z1}$  = 29,322.81 steps<sup>2</sup>/Ws:

(INTRPTLEVL) =

$$\frac{3 \text{ [kW] x } 4096 \text{ x } 29,322.81 \text{ [steps}^2/\text{Ws]}}{2 \text{ [kHz]}} =$$

= 180,159,344.6  $\approx$  0x0ABD,0370

Example: ILREACHEDFG is to be set after 8192 measurements. The value in INTRPTLEVL is 0x2000 (INTRPTLEVL\_LO = 0x2000, INTRPTLEVL\_HI = 0x0). ILREACHEDFG is set every 2s if  $f_{ADC}$  = 4096Hz.

#### ESP430CE1A

Works for both positive and negative energies and is indicated by the flag ILNEGFG.

#### **Note: Return Register Updates**

When the interrupt level is reached, only ILREACHEDFG is set; the update of the return registers is not affected.

#### **CALCYCLCNT: Calibration Cycle Count**

CALCYCLCNT defines the number of mains frequency periods used for calibration when the ESP430CE1 is set to Calibration Mode.

| Format         | Unsigned integer | +16.0             |

|----------------|------------------|-------------------|

| Range          | 0x00 to 0xFFFF   | 0 to 65,535       |

| Normal Range   | 0x01 to 0x200    | 1 to 512          |

| Resolution     | 1 mains period   |                   |

| Initialization | 0x64             | 100 mains periods |

Example: The calibration cycle count required is determined to be 40 mains cycles. The value stored in CALCYCLCNT is 0x0028.

#### STARTCURR: Energy Measurement Start Current

#### **ESP430CE1**

STARTCURR (STARTCURR = STARTCURR\_INT.STARTCURR\_FRAC = 32-bits) defines the current threshold at which energy accumulation is performed when the ESP430 is not in calibration mode. If the measured current's RMS value is below the threshold defined by STARTCURR, no energy is accumulated.

When both I channels are used, the greater current value of  $I_1$  and  $I_2$  is used and is indicated by I2GTI1FG. In this configuration, when one  $I_X$  value is above the STARTCURR threshold, energies for both channels are accumulated.

| Format         | Unsigned Integer.Fraction               | +15.16                 |

|----------------|-----------------------------------------|------------------------|

| Range          | 0x0.0 to 0x07FFF.FFFF                   | 0.0 to +32767.9999     |

| Normal Range   | 0x00 to 0x666.C000                      | 0 to 5.0 %             |

| Resolution     | ±0.25 steps are used for the comparison |                        |

| Initialization | 0x17.2A90                               | 0.1 % × 0x7FFF × 0.707 |

Formulas:

$$(STARTCURR) = \frac{I_{START}}{k_{lcom}} \times 2^{16}$$

Example: The required start current for an electricity meter is 40 mA. The value for STARTCURR is:

(STARTCURR) =

$$\frac{40 \text{ [mA]}}{2.21946 \text{x} 10^{-3} \text{ [A/step]}} \text{ x } 2^{16} =$$

= 1, 181, 116.127 = 0x0012, 05BC

#### **Note: STARTCURR Comparison**

The 16-bit value in STARTCURR\_INT and the two MSBs in STARTCURR\_FRAC are used for the  $I_X$  comparison. The remaining LSBs are ignored.

#### ESP430CE1A

The value in STARTCURR defines the current value for the start of the energy counting if the Operation Mode is not set to Calibration. Below this value all calculated energies (active energy, reactive energy and apparent energy) provided for the CPU are zero. The RMS value of the measured current I is used. For a better resolution the fractional part is also defined. For the comparison the (IRMS) value is used: the flag I2GTI1FG defines if the result for I1RMS or I2RMS was stored there.

| Format         | Unsigned Integer.Fraction    | +15.16                             |

|----------------|------------------------------|------------------------------------|

| Range          | 0x0.0 to 0x07FFF.FFFF        | 0.0 to +32767.9999                 |

| Normal Range   | 0x00 to 0x666.5999           | 0 to 5.0%                          |

| Resolution     | All 32 bits are used for the |                                    |

|                | comparison                   |                                    |

| Initialization | 0x17.45A1                    | $0.1\% \times 0x7FFF \times 0.707$ |

Formulas:

$$(IRMS) = \frac{\sqrt{(ACTENERGY1)^2 + (REACTENERGY)^2}}{(VRMS)} \quad [steps] \quad \text{if I2GTI1FG} = 0$$

$$(IRMS) = \frac{\sqrt{(ACTENERGY2)^2 + (REACTENERGY)^2}}{(VRMS)} \quad [steps] \quad \text{if I2GTI1FG} = 1$$

$$(STARTCURR) = \frac{I_{START}}{k_{lcom}} \times 2^{16}$$

Example 1: See Example for ESP430CE1.

Example 2: The required start current for an electricity meter is 40 mA. The value for STARTCURR is:

(STARTCURR) =

$$\frac{I_{START}}{k_{I1}} \times 2^{16} = \frac{40 \text{ [mA]}}{2.21946 \text{x} 10^{-3} \text{ [A/step]}} \times 2^{16} =$$

= 1,181,116.127 = 0x0012,05BC

The value for STARTCURR is 0x05BC (to LSBs at address STARTCURR) and 0x0012 (to MSBs at address STARTCURR + 2). All 16 bits (0x05BC) at the address STARTCURR are used for the comparison.

#### **NOMFREQ: Nominal Mains Frequency**

NOMFREQ defines the expected nominal line, or mains, frequency. The mains frequency is required for ESP430 phase correction of DC tolerant current transformers using PHASECORRx.

| Format         | Unsigned Integer | +8.0        |

|----------------|------------------|-------------|

| Range          | 0x00 to 0x0FF    | 0 to +255   |

| Normal Range   | 0x28 to 0x46     | 40 to 70 Hz |

| Resolution     | 1 Hz             |             |

| Initialization | 0x32             | 50 Hz       |

Example: The expected mains frequency is 60 Hz corresponding to NOMFREQ = 0x3C.

#### **VDROPCYCLS: Voltage Drop Detection Cycles**

VDROPCYCLS defines the maximum number of contiguous mains voltage cycles having an absolute peak value less than the threshold defined by VDROPLEVEL. If the number of low voltage mains voltage cycles reaches the VDROPCYCLS, VDROPFG in ESP430\_STAT0 is set. VDROPFG is reset when the absolute peak level of the voltage is greater than the value in VDROPLEVEL.

| Format         | Unsigned Integer | +8.0                    |

|----------------|------------------|-------------------------|

| Range          | 0x00 to 0x0FF    | 0 to +255 mains periods |

| Normal Range   | Full range       |                         |

| Resolution     | 1 mains period   |                         |

| Initialization | 0x05             | 5 mains periods         |

#### Formulas:

```

\begin{split} & \text{If } |(\text{WAVESFSV1})| \geq (\text{VDROPLEVEL}): \text{ VDROPFG} = 0, \text{vdrop}_{\text{cnt}} = 0 \\ & \text{If } |(\text{WAVESFSV1})| < (\text{VDROPLEVEL}): \text{ vdrop}_{\text{cnt}} = \text{vdrop}_{\text{cnt}} + 1 \\ & \text{If } \text{vdrop}_{\text{cnt}} \geq (\text{VDROPCYCLS}): \text{VDROPFG} = 1 \end{split}

```

#### **RATIOTAMP: Tampering Current Ratio**

RATIOTAMP defines the threshold for the ratio of the internal ESP430 currents  $I_{1RMS}$  and  $I_{2RMS}$  used to indicate potential meter tampering. This feature is valid for the Energy Plus Tamper Detection configuration only. Both RMS currents are calculated and the greater of the two is stored in IRMS. TAMPFG in ESP430\_STAT0 is set according to the comparison and depends on I2GTI1FG:

```

TAMPFG = 0: (no tampering) when:

```

```

- I2GTI1FG = 0:I<sub>1RMS</sub> < I<sub>2RMS</sub> × (RATIOTAMP) × 2<sup>-14</sup>

- I2GTI1FG = 1: I<sub>2RMS</sub> < I<sub>1RMS</sub> × (RATIOTAMP) × 2<sup>-14</sup>

```

TAMPFG = 1: (potential tampering occurred) when:

```

- I2GTI1FG = 0: I_{1RMS} ≥ I_{2RMS} × (RATIOTAMP) × 2<sup>-14</sup>

```

- I2GTI1FG = 1:  $I_{2RMS}$  ≥  $I_{1RMS}$  × (RATIOTAMP) × 2<sup>-14</sup>

When hardware implementations for I<sub>1</sub> and I<sub>2</sub> vary, adaptation for the two channels may be required in order to get equivalent results under equivalent excitation. Refer to the ADAPTI1 and ADAPTI2 sections for more information.

| Format         | Unsigned Integer.Fraction | +1.14               |

|----------------|---------------------------|---------------------|

| Range          | 0x4000 to 0x7FFF          | 1.0 to +1.999938965 |

| Normal Range   | Full range                |                     |

| Resolution     | 61.035x10 <sup>-6</sup>   | 2-14                |

| Initialization | 0x4000                    | 1.000               |

Formulas:

$$(RATIOTAMP) = \left(\frac{I_{HI}}{I_{LO}}\right)_{MAX} X 2^{14}$$

Where:

$I_{HI}$ : Larger RMS value of  $I_{1RMS}$  and  $I_{2RMS}$   $I_{LO}$ : Smaller RMS value of  $I_{1RMS}$  and  $I_{2RMS}$

Example: When  $I_X$  RMS currents differ by more than 5 %, potential tampering has occurred. RATIOTAMP is:

(RATIOTAMP) =

$$\left(\frac{1.05}{1.00}\right)$$

x  $2^{14} = 17,203.2 \approx 0$ x 4333

Note:  $I_X$  RMS Results and TAMPFG

When IRMS is less than the threshold set in ITAMP, TAMPFG = 0 and will not be set regardless of the measured RMS ratio for  $I_1$  and  $I_2$ .

#### **ITAMP: Tampering Current Threshold**

ITAMP defines the RMS current threshold for  $I_1$  and  $I_2$  enabling the ESP430 to perform a tampering check using RATIOTAMP. This feature is valid for the Energy Plus Tamper Detection configuration only.

| Format         | Unsigned Integer | +15.0                  |

|----------------|------------------|------------------------|

| Range          | 0x00 to 0x07FFF  | 0.0 to +32,767         |

| Normal Range   | Full range       |                        |

| Resolution     | 1 step           |                        |

| Initialization | 0x2E             | 0.2 % × 0x7FFF × 0.707 |

Formulas:

$$(ITAMP) = \frac{I_{TAMP}}{k_{Icom}}$$

Where:

I<sub>TAMP</sub>: Current threshold for tamper check

k<sub>Icom</sub>: Common meter constant

Example: No tampering check to be made below 2% of the specified 40 A maximum RMS current for the meter.  $k_{lcom}$  = 0.0025 A/step. ITAMP is:

$$(ITAMP) = \frac{40 \times 0.02}{0.0025} = 320.0 = 0 \times 140$$

#### **VDROPLEVEL: Voltage Drop Detection Threshold Level**

VDROPLEVEL defines the minimum absolute peak value of the mains voltage  $V_1$  expected during a normal mains period. If VDROPLEVEL is not reached, an internal ESP430 counter increments. When this counter reaches the value in VDROPCYCLS, VDROPFG = 1.

| Format       | Unsigned Integer | +15.0          |

|--------------|------------------|----------------|

| Range        | 0x00 to 0x07FFF  | 0.0 to +32,767 |

| Normal Range | Full range       |                |

| Resolution   | 1 step           |                |

Formulas:

(VDROPLEVEL) =

$$\frac{|V_{1PEAK}|}{k_{V1}} = \frac{|V_1| \times \sqrt{2}}{k_{V1}}$$

(for sinusoidal voltage)

Example: VDROPFG should be set when  $V_1$  falls below 75% of the nominal voltage of 230 V for 6 or more mains periods,  $k_{V1} = 15.365513x10^{-3}$ . VDROPCYCLS = 0x6, VDROPLEVEL is:

(VDROPLEVEL) =

$$\frac{|230 \times 0.75| \times \sqrt{2}}{15.365513 \times 10^{-3}} = 15,876.58 \approx 0 \times 3E05$$

#### Note: VDROPFG and V1RMS

When V1RMS is less than 0.088\*VDROPLEVEL, VDROPFG will be set independent of the internal ESP430 counter used for VDROPLEVEL.

#### **VPEAKLEVEL: Voltage Peak Level**

VPEAKLEVEL defines the maximum value for  $V_1$ . If the absolute value of the measured voltage is greater than VPEAKLEVEL, V1PEAKFG = 1, otherwise V1PEAKFG = 0. To filter out single spikes on the line, three contiguous measurements must exceed VPEAKLEVEL.

| Format         | Unsigned Integer | +15.0                 |

|----------------|------------------|-----------------------|

| Range          | 0x00 to 0x07FFF  | 0.0 to +32,767        |

| Normal Range   | Full range       |                       |

| Resolution     | 1 step           |                       |

| Initialization | 0x7FFF           | Maximum voltage value |

Formulas:

$$(VPEAKLEVEL) = \frac{|V_{1MAX}|}{k_{V1}}$$

Where V<sub>1MAX</sub>: Maximum V<sub>1</sub> peak voltage

Example:  $V_{1MAX}$  is specified to be  $\pm 398V$ ;  $k_{V1} = 15x10^{-3}$ . VPEAKLEVEL is:

$$(\text{VPEAKLEVEL}) = \frac{|V_{\text{1MAX}}|}{k_{\text{V1}}} = \frac{398[V]}{15x10^{-3} \, [V/\text{step}]} \approx 0x67A5$$

V1PEAKFG = 1 if three contiguous, voltage samples greater than 0x67A5 or less than 0x985B are measured (0x985B = -0x67A5), else V1PEAKFG = 0.

#### **IPEAKLEVEL: Current Peak Level**

IPEAKLEVEL defines the maximum value for  $I_1$  and  $I_2$ . If the absolute value of each measured current is greater than IPEAKLEVEL, IxPEAKFG = 1, otherwise IxPEAKFG = 0, where x = 1 or 2 for  $I_1$  or  $I_2$ , respectively. To filter out single spikes on the line, three contiguous measurements must exceed IPEAKLEVEL.

| Format         | Unsigned Integer | +15.0                 |

|----------------|------------------|-----------------------|

| Range          | 0x00 to 0x07FFF  | 0.0 to +32,767        |

| Normal Range   | Full range       |                       |

| Resolution     | 1 step           |                       |

| Initialization | 0x7FFF           | Maximum current value |

Formulas:

$$(IPEAKLEVEL) = \frac{|I_{max}|}{k_{lcom}}$$

Example: I1PEAKFG = 1 when a current sample greater than 42A\*1.414 (peak value for 42A) is measured on  $I_1$ ,  $k_{lcom1} = 0.0025$  A/step. IPEAKLEVEL is:

(IPEAKLEVEL) =

$$\frac{\left|42 \text{ x } \sqrt{2}\right|}{2.5 \text{x} 10^{-3} \left[\text{A/step}\right]} = 23,758.79 \approx 0 \text{x} 5 \text{CCE}$$

#### **DCREMPER: DC Removal Period Count**

DCREMPER defines the number of mains periods used for one iteration of the DC removal algorithm. Larger values in DCREMPER may improve noise suppression and result in longer calculation settling times. When the DC removal function is disabled, DCREMPER is not used.

If the dc removal function is not switched on (with bits DCREM\_V1, DCREM\_I1, DCREM\_I2):

ESP430CE1: The offset measured with shorted ADC inputs during the initialization (or with the INIT Control Command) is used.

ESP430CE1A: The value 0 is used.

| Format         | Unsigned Integer | +6.0                                         |

|----------------|------------------|----------------------------------------------|

| Range          | 0x00 to 0x032    | 0 to +50 (due to 32-bit sum buffer capacity) |

| Resolution     | 1 mains period   |                                              |

| Initialization | 0x05             | 5 mains periods                              |

#### DC Removal Function Description

If the AFE voltage and current samples contain offsets or DC components, the measured energy W is:

$$\begin{split} W &= \frac{1}{f_{ADC}} \times \sum_{t=0}^{t=\infty} (v_n + v_{dc}) \times (i_n + i_{dc}) = \\ &= \frac{1}{f_{ADC}} \times \sum_{t=0}^{t=\infty} (v_n \times i_n + v_n \times i_{dc} + i_n \times v_{dc} + i_{dc} \times v_{dc}) \end{split}$$

Where:

$v_{dc}$  = DC part of a voltage sample [V]

i<sub>dc</sub> = DC part of a current sample [A]

v<sub>n</sub> = voltage sample [V]

i<sub>n</sub> = current sample [A]

**NOTE:** With the ESP430CE1A, a watchdog is implemented for a missing voltage V<sub>1</sub>. See section "Zero Crossing watchdog".

The terms  $(v_n \times i_{dc})$  and  $(i_n \times v_{dc})$  in the above equation equal zero when summed over one full mains period (the integral of a sine wave from 0 to  $2\pi = 0$ ). However the term  $(i_{dc} \times v_{dc})$  is added erroneously to the energy summation with each sample result. If one of the two offsets can be set to zero, the error term is eliminated.

With the DC removal function enabled, it is possible to eliminate the DC component for the V<sub>1</sub> voltage path or the current paths, I<sub>1</sub> and I<sub>2</sub>. DCREMPER defines the number of mains periods used for the calculation of the DC removal values.

#### 1.2.9 Detection of Zero Crossing

#### Zero Crossing Checks

Zero crossing of the voltage  $V_1$  is detected by the change of the sign of  $V_1$  after two samples with the same sign:

- Leading edge: a positive V<sub>1</sub> sample follows two negative ones.

- ☐ Trailing edge: a negative V<sub>1</sub> sample follows two positive ones.

#### **ESP430CE1A Only**

To get secure results with noise and spikes on the voltage  $V_{1}$ , two limits are given for the change of  $V_{1}$ :

- ☐ The two V<sub>1</sub> samples before and after the sign change must have minimum distances of 502 ADC steps. This avoids noise induced, false zero crossings.

- □ V1FILTER enabled: Spikes of  $V_1$  are checked against the value (DELTAV1MAX) in the Parameter Registers. The voltage sample differences  $|\Delta N_{V1}|$  must be smaller than (DELTAV1MAX), otherwise a linear approximation is used for the actual  $V_1$  sample v1n.

The V1FILTER avoids false zero crossings by large spikes.

If V1FILTER = 0:

No V<sub>1</sub> check is made. Sample v1n is used as it is.

If V1FILTER = 1:

If  $|N_{v1n} - N_{v1n-1}| < (DELTAV1MAX)$ , sample v1n is used as it is.

Else  $N_{v1n} = (N_{v1n-1} - N_{v1n-2}) + N_{v1n-1} = 2N_{v1n-1} - 2N_{v1n-2}$ , a linear approximation for sample v1 is used.

If the V1FILTER is used, the value for (DELTAV1MAX) must be set by the CPU to the maximum dv1/dt value for the used ADC range, multiplied with a security factor k<sub>safety</sub>, e.g., 1.2:

(DELTAV1MAX) =

$$2\pi \times f_{\text{mains max}} \times \frac{N_{\text{ADC max}}}{f_{\text{ADC}}} \times k_{\text{safety}}$$

Example: The V1FILTER is used with a used ADC range of 90 %, a maximum mains frequency of 51 Hz, an ADC frequency of 4096 Hz and a safety factor 1.1. The value in DELTAV1MAX is:

(DELTAV1MAX) =

$$2\pi \times 51 \times \frac{0.9 \times 7FFFh}{4096} \times 1.1 = 2538$$

#### Zero Crossing Watchdog (ESP430CE1A Only)

With V1 disconnected, no zero crossings occur and no mains period measurements are made. To allow the important dc removal calculations without V1, a watchdog is implemented for the zero crossing detection. This Zero Crossing Watchdog is reset with each detected valid zero crossing of V1 and incremented with the sample frequency  $f_{\mbox{ADC}}$ . If the watchdog reaches the fixed value:

$$ZCWD = \frac{f_{ADC max}}{f_{mains min}} + k_{ZCWD} = \frac{4096}{40} + 40 \approx 142$$

the dc removal calculations are processed with the accumulated values and the watchdog is reset.

The maximum repetition frequency f<sub>DCRmmax</sub> of the dc removal function due to the Zero Crossing Watchdog is:

$$f_{DCRm max} = \frac{f_{ADC}}{(DCREMPER) \times ZCWD} + 1 [Hz]$$

With the initial value of 5 for (DCREMPER) and  $f_{ADC} = 4096$  Hz this leads to:

$$f_{DCRm \, max} = \frac{4096}{5 \times 142} + 1 \simeq 6 \, [Hz]$$

The dc removal function is called with a repetition frequency of 6 Hz if  $V_1$  is missing.

With the safety function of the Zero Crossing Watchdog, energy measurements are still possible without V1 connected: the correctly measured value IRMS is multiplied by a defined value for  $V_1$ , e.g., 100%. The multiplication and accumulation is made by the CPU in this case.

#### 1.2.10 Common Mode Rejection (ESP430CE1A Only)

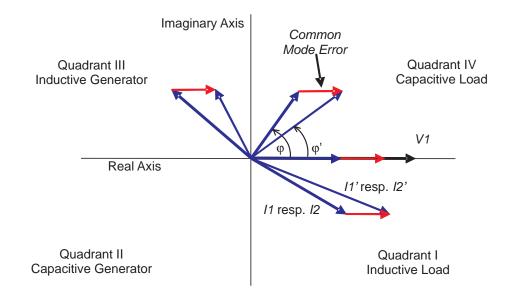

Figure 1–4 shows the common mode influence of the voltage V1 to the currents I1 and I2. This influence is only visible at very low currents. The common mode influence is a constant error value (shown red in the next figure) in phase with the voltage V1. The common mode influence changes the phase angle  $\phi$  to  $\phi'$  and the current values from  $I_1$  and  $I_2$  to  $I_1'$  and  $I_2'$  dependent on the quadrant of the current.

These two changes introduce a measurement error which depends on the phase angle  $\varphi$  and the current value.

Figure 1-4. Common-Mode Influence to the Current Path

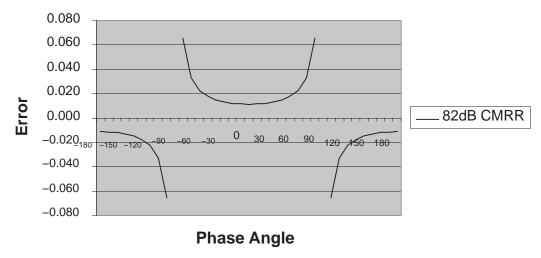

Figure 1–5 shows the dependence of the measurement error to the phase angle  $\varphi$ . It is described by the  $\cos^{-1}\varphi$  function.

Figure 1-5. E-Meter Error Due to CMRR

Due to the constant value and phase angle of the introduced common mode error, it is possible to correct this error: it is only necessary to subtract its value from all measured active energy values.

The value in address CMRRCOMP controls the common mode rejection function of the ESP430CE1A:

- ☐ If (CMRRCOMP) = 0: the common mode rejection function is switched off.

- ☐ If (CMRRCOMP) > 0: the value is a quarter of the actual value to be used. This is to allow also the compensation of small common mode influences.

The value in CMRRCOMP is approximately given by:

(CMRRCOMP) =

$$0.25 \times 10^{(0.05 \times CMRR)}$$

The compensation value (CMRRCOMPStore) for the active energies is calculated with the formula:

$$(CMRRCOMPStore) = \frac{(V1RMS)^2}{4 \times (CMRRCOMP)}$$

(CMRRCOMPStore) is used for the correction of all measured active energies:

- Active energy for 4096 samples (ACTENERGY1 and ACTENERGY2). The common mode correction is made with the value for (CMRRCOMPStore) of the actual 4096 samples.

- ☐ Active energy for a single mains period (ACTENSPER1 and ACTENSPER2). The common mode correction is made with the value for (CMRRCOMPStore) of the last 4096 samples, not of the actual ones: the actual value of (CMRRCOMPStore) is not yet available.

- □ Active energy used with bit ILREACHEDFG if bit MB = 0 (ILREACHEDFG is set dependent on the reached energy level). The common mode correction is made with the value for (CMRRCOMPStore) of the last 4096 samples, not of the actual ones: the actual value for (CMRRCOMPStore) is not yet available.

The reactive energy is not influenced by the common mode and, therefore, needs no correction.

The apparent energy is calculated with the corrected active energy and the not influenced reactive energy, and is also correct.

#### 1.2.11 Maximum Spike for V<sub>1</sub> Filter (ESP430CE1A Only)