VLSI Engineering and Design Automation Division Seminar WUT - November 16, 2007, Warsaw, Poland

# Studying CMOS Defects with DefSim

**Overview and Demonstration**

A. Jutman<sup>1</sup>, W. A. Pleskacz<sup>2</sup>

<sup>1</sup>Tallinn University of Technology, Estonia <sup>2</sup>Warsaw University of Technology, Poland artur@pld.ttu.ee, pleskacz@imio.pw.edu.pl

- Introduction and Motivation

- Implementation of defects

- DefSim chip structure and design

- DefSim in a lab and classroom

- Experiments with defects and models

- DefSim software

- Conclusions and Future work

# **Project Funding**

Financial support for DefSim hardware development was provided by:

- REASON (IST-2000-30193), an IST project funded by the European Union;

- Polish State Committee for Scientific Research (project No. 4 T11B 023 24);

- Estonian Science Foundation grants G5649, G5910 and Enterprise Estonia.

DefSim Personal and DefSim Server software was developed by Testonica Lab free of charge

# Project Team

Warsaw University of Technology

Coordinator: Dr. Witold PleskaczT. BorejkoT. GugalaP. PizonA. WalkanisP. TrochimiukK. Bolczak

X

Coordinator: Prof. Raimund Ubar

- A. Jutman

- S. Devadze

- E. Orasson

Dr. Viera Stopjakova

The team would like to thank Prof. W. Kuzmicz from Warsaw University of Technology for his support and valuable feedback

ITRS: testing is already one of key problems in current generation of VLSI chips and its importance will be growing.

M

- There is a strong demand for well-educated specialists in the area of IC testing.

- Teaching of testing topics is based on abstract models which do not reflect well physical reality.

- Simulation alone is not sufficient, "real silicon" is needed for better understanding of test problems and for training in fault simulation and test pattern generation.

Development of a VLSI chip providing practical possibility for testing real circuits with *artificially introduced* but *real* physical defects, and in particular:

- demonstration of defects that are not easy to be modeled or for which existing fault models do not follow the real electrical effect of the respective defect precisely,

- testing of simple gates as well as gates embedded in larger digital circuits,

- comparison of theoretical and real defect coverage for various sets of test vectors,

- demonstration of  $I_{DDQ}$  testing and its efficiency,

- making the chip "student-proof" and avoiding possible damage resulting from its operation with intentionally introduced defects.

Created environment can be used in research also (e.g. in evaluation of defect-oriented test pattern generation methods and tools).

## Implementation of defects

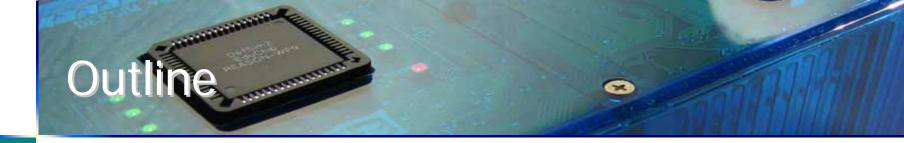

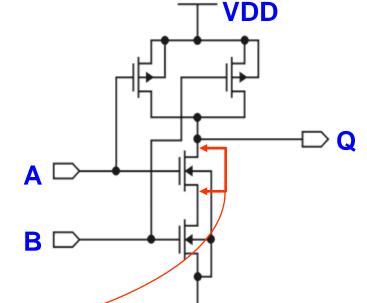

#### Complex cell with IN-OUT short

## Implementation of defects

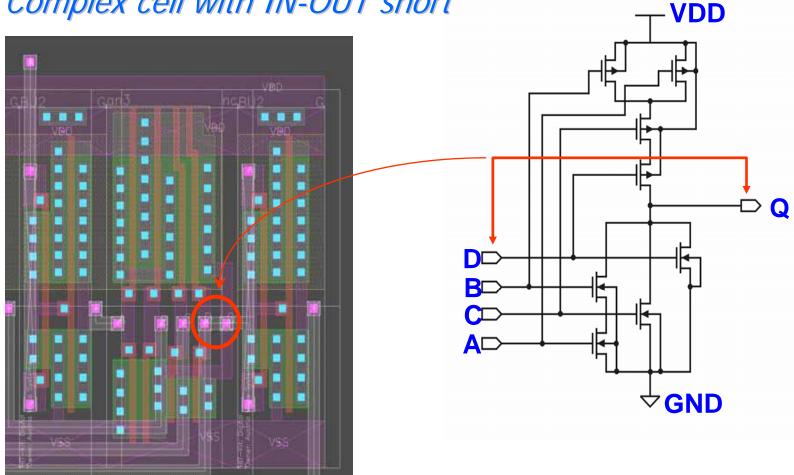

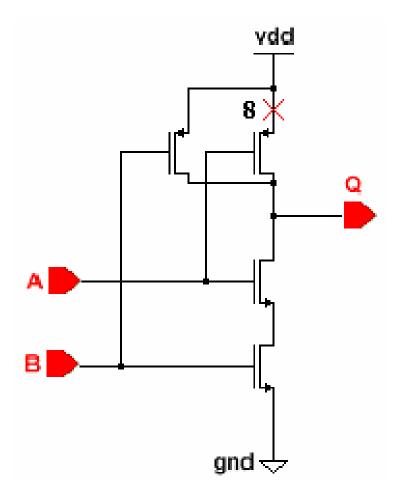

#### NAND2 cell with floating gate

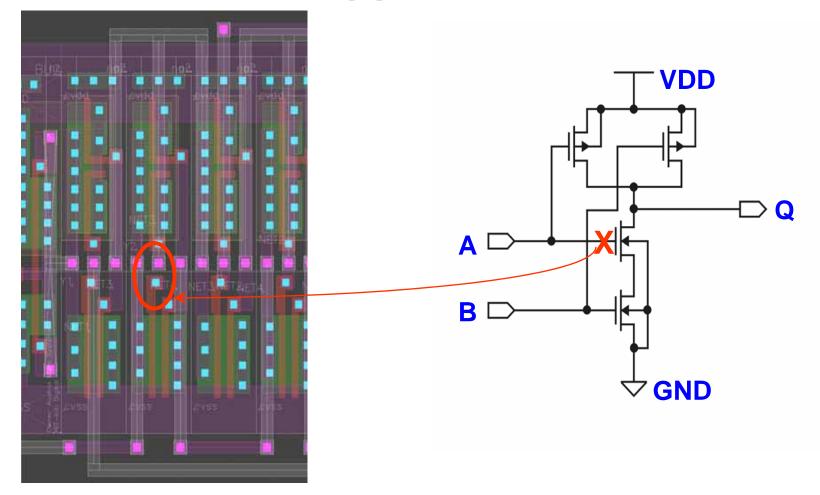

## Implementation of defects

#### NAND2 cell with D-S short (missing poly)

- Altogether there are over 500 different defects on the chip

- Implemented defects are shorts and opens in metal and poly layers

- To be close to the silicon reality each cell is loaded and driven by standard non-inverting buffers

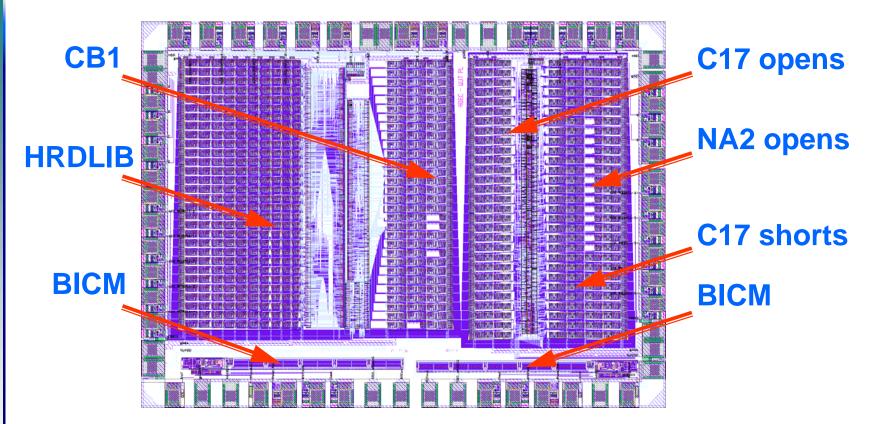

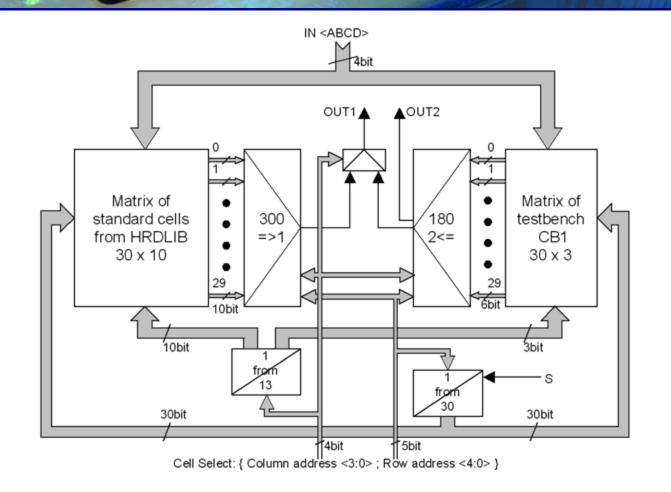

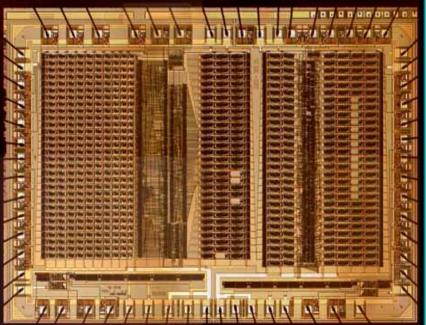

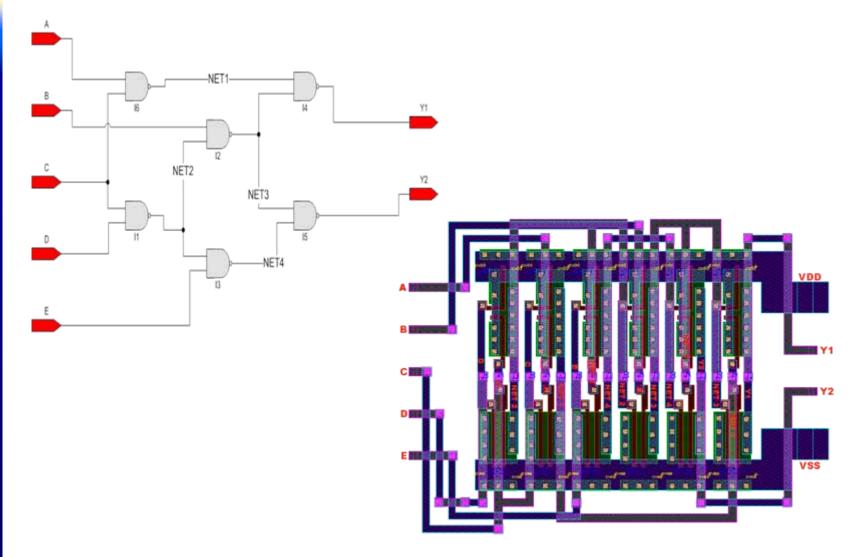

# DefSim IC layout

X

16 different complex cells and small circuits implemented For each cell there is a fault-free circuit and many copies of the same cell with intentionally injected defects.

Schematic diagram of block1

Only one circuit at a time can be active (selected)

# DefSim IC details

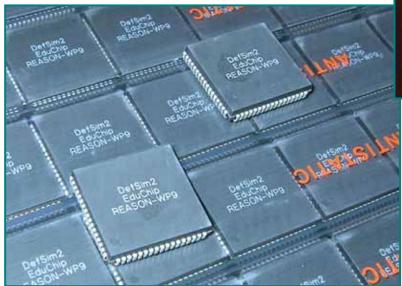

- Standard industrial technology (AMS CMOS 0.8µm CYE - 2M/2P)

- Area 19.90 mm<sup>2</sup>

- Approx. 48000 transistors

- 62 pins, JLCC68 package

A built-in current monitor for  $I_{DDQ}$  testing is implemented in each block.

## DefSim Cell Examples: c17

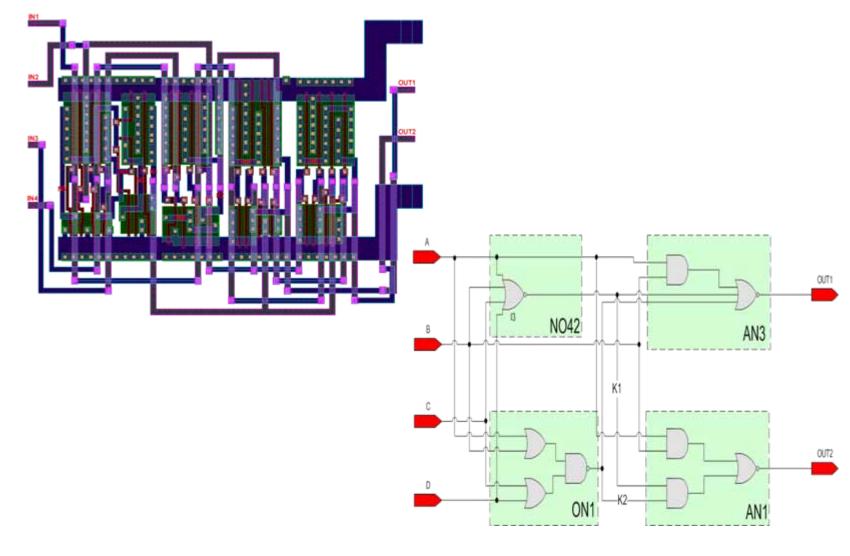

## DefSim Cell Examples: CB\_1

## DefSim in the classroom .

### With DefSim you can

- Observe the truth table of correct circuit

- Observe the truth table of defective circuit

- Obtain defect/fault tables for all specific defects

- Define test patterns automatically or manually

- Activate IDDQ and voltage measurements

- Study behavior of bridging and open faults

- Study and compare different fault models

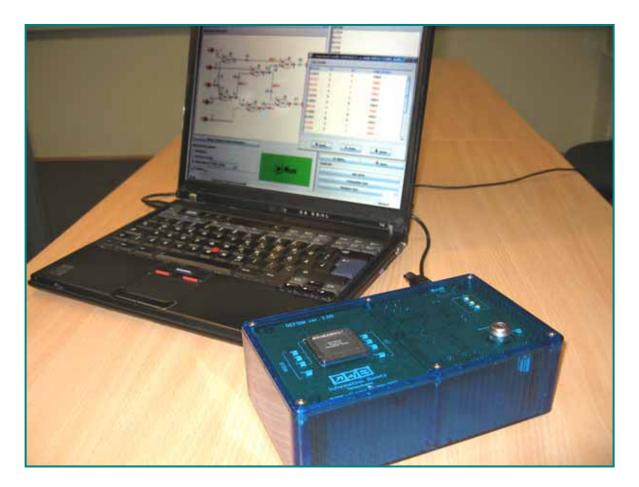

# Lab environment

×

#### "Plug and Play" – dedicated hardware and software

**DefSim software**

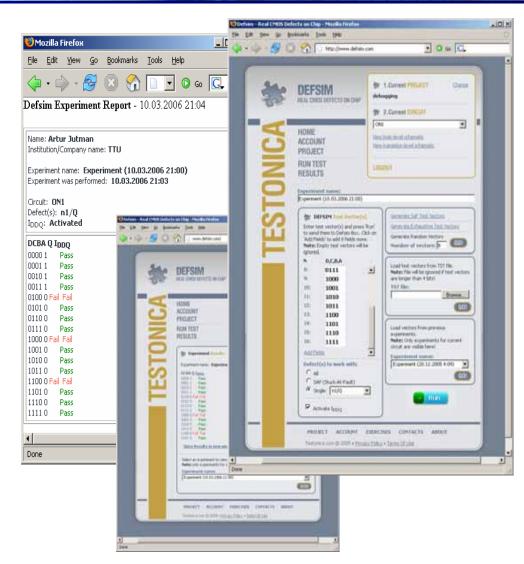

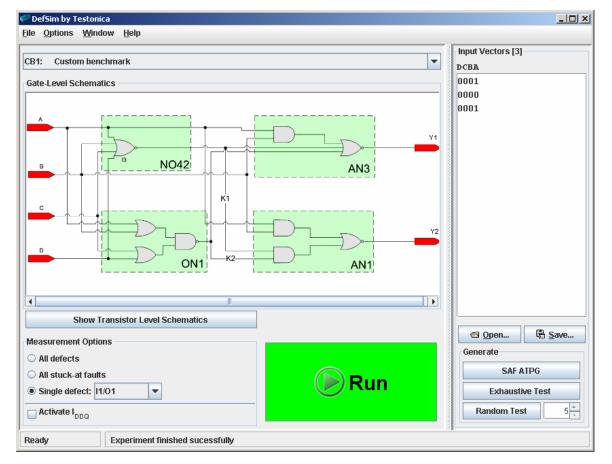

# DefSim Personal – *simple but powerful*.

X

Personal solution allows to experiment with different aspects of IC testing shortly after connecting DefSim hardware with computer. Ideal for standalone use or for small groups of users.

## **DefSim software**

#### DefSim Server – *advantage by sharing*.

Built on a top of modern Web-technologies DefSim Server is capable to share single or several hardware devices between multiple users. Best suitable for organizing study process in classrooms, distance e-learning or remote Web-access services.

X

# Outline

- Introduction and Motivation

- Implementation of defects

- DefSim chip structure and design

- DefSim in a lab and classroom

- DefSim software

- Experiments with defects and models

- Conclusions and Future work

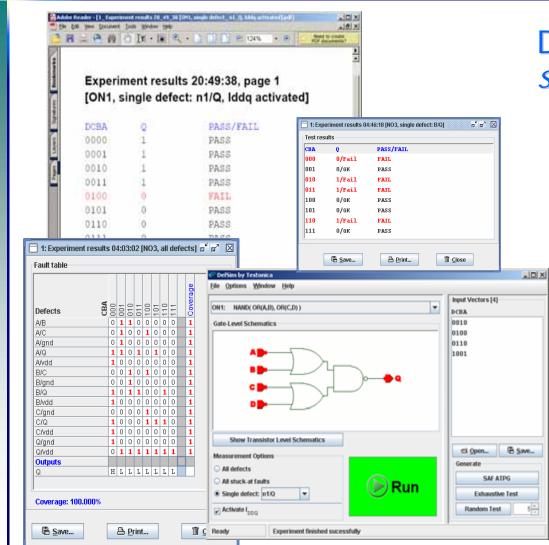

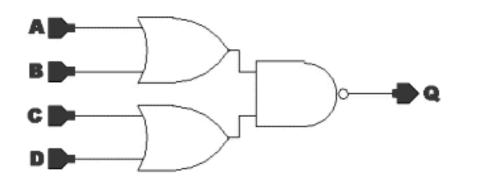

#### Evaluating stuck-at fault model

\_ 🗆 🗵 **DefSim by Testonica** File Options Window Help Input Vectors [4] NAND( OR(A,B), OR(C,D) ) Ŧ ON1: DCBA 0010 Gate-Level Schematics 0100 0110 1001 Show Transistor Level Schematics B Save... 🚭 Open... Measurement Options Generate All defects SAF ATPG All stuck-at faults Run Single defect: A/B Exhaustive Test 5 Activate I DDQ Random Test Experiment finished sucessfully Ready

#### Evaluating stuck-at fault model

#### Evaluating stuck-at fault model

#### Either 0101 or 1010 vector need to be added

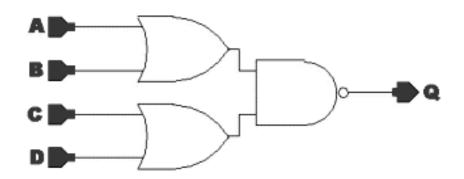

#### Bridging faults: wired-AND or wired-OR?

Complex gate ON1, defect: B/C

| Teet | wired AND | wired OR |

|------|-----------|----------|

| Test | DCBA      | DCBA     |

| 1    | 1010      | 1100     |

| 2    | 0101      | 0100     |

| 3    |           | 0011     |

| 4    |           | 0010     |

#### Bridging faults: wired-AND or wired-OR?

| DCBA<br>0000                      | <mark>0</mark><br>1/ок        | PASS/FAIL<br>PASS    |                   |      |           |          |

|-----------------------------------|-------------------------------|----------------------|-------------------|------|-----------|----------|

| 0000<br>0001<br>0010              | 1/0К<br>1/0К<br>1/0К          | PASS<br>PASS<br>PASS |                   |      | wired AND | wired OR |

| 0011<br>0100                      | 1/0К<br>1/0К                  | PASS<br>PASS         |                   | Test | DCBA      | DCBA     |

| <mark>0101</mark><br>0110<br>0111 | <b>1/Fail</b><br>0/ок<br>0/ок | FAIL<br>PASS<br>PASS |                   | 1    | 1010      | 1100     |

| 1000<br>1001                      | 0/0К<br>1/0К<br>0/0К          | PASS<br>PASS<br>PASS | > failed patterns | 2    | 0101      | 0100     |

| 1010<br>1011                      | 0/0К<br>1/Fail<br>0/0К        | FAIL                 | patterns          | 3    |           | 0011     |

| 1100<br>1101                      | 1/ок<br>0/ок                  | PASS                 |                   | 4    |           | 0010     |

| 1110<br>1111                      | 0/0K<br>0/0K                  | PASS                 |                   |      | I I       |          |

#### Wired AND model describes this defect

#### Bridging faults: further study

Complex gate ON1, defect: D/Q

| Toot | wired AND | wired OR |

|------|-----------|----------|

| Test | DCBA      | DCBA     |

| 1    | 0000      | 0001     |

| 2    | 0001      | 0010     |

| 3    | 0010      | 0011     |

| 4    | 0011      | 1001     |

| 5    | 0100      | 1010     |

| 6    | 1001      | 1011     |

| 7    | 1010      | 1101     |

| 8    | 1011      | 1110     |

| 9    |           | 1111     |

#### Bridging faults: further study

| ] 1: Exper<br>Test resul |        | 08:56 [ON1, single defect: D/Q] | X |

|--------------------------|--------|---------------------------------|---|

| DCBA                     | 0      | PASS/FAIL                       | - |

| 0000                     | 0/Fail | FAIL                            | • |

| 0001                     | 0/Fail | FAIL                            |   |

| 0010                     | 0/Fail | FAIL                            |   |

| 0011                     | 0/Fail | FAIL                            |   |

| 0100                     | 0/Fail | FAIL                            |   |

| 0101                     | 0/0K   | PASS                            |   |

| 0110                     | 0/0K   | PASS                            |   |

| 0111                     | 0/0K   | PASS                            | _ |

| 1000                     | 1/0K   | PASS                            |   |

| 1001                     | 1/Fail | FAIL                            |   |

| 1010                     | 1/Fail | FAIL                            |   |

| 1011                     | 1/Fail | FAIL                            |   |

| 1100                     | 1/0K   | PASS                            |   |

| 1101                     | 1/Fail | FAIL                            |   |

| 1110                     | 1/Fail | FAIL                            |   |

| 1111                     | 1/Fail | FAIL                            | - |

|                          | 🖷 Save | 🕒 <u>P</u> rint 🛅 <u>C</u> lose |   |

| Test | wired AND | wired OR |

|------|-----------|----------|

| 1621 | DCBA      | DCBA     |

| 1    | 0000      | 0001     |

| 2    | 0001      | 0010     |

| 3    | 0010      | 0011     |

| 4    | 0011      | 1001     |

| 5    | 0100      | 1010     |

| 6    | 1001      | 1011     |

| 7    | 1010      | 1101     |

| 8    | 1011      | 1110     |

| 9    |           | 1111     |

#### Neither wired AND nor wired OR!? Victim-aggressor behavior: D is a stronger driver!

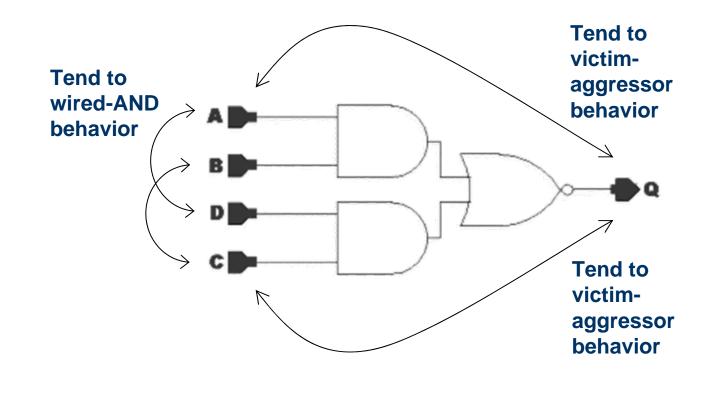

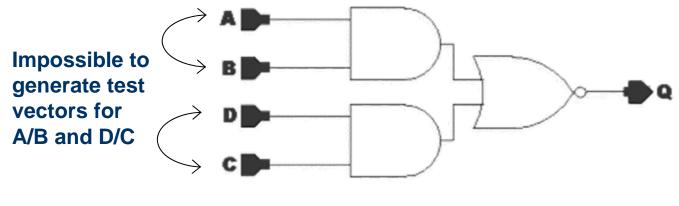

#### Behavior of shorts in DefSim

*I*<sub>DDQ</sub> versus voltage testing

**Complex gate AN1**

#### *I*<sub>DDQ</sub> versus voltage testing

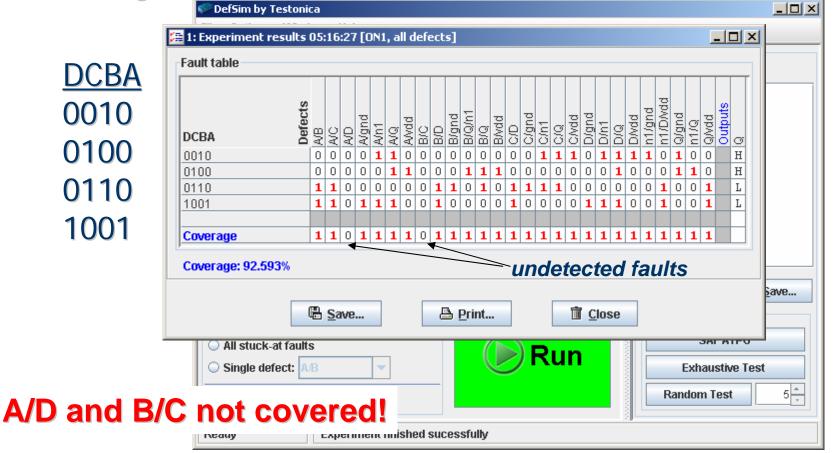

#### Impossible generate te vectors for A/B and D/

|                     | 🚝 1: Experiment resu | ults 03:16:0          | 7 [AN1      | , all d           | efec | ts]           |             |                 |       |      |               |       |      |     |       |               |        |       |            | _ [     | 그.     |

|---------------------|----------------------|-----------------------|-------------|-------------------|------|---------------|-------------|-----------------|-------|------|---------------|-------|------|-----|-------|---------------|--------|-------|------------|---------|--------|

|                     | Fault table          |                       |             |                   |      |               |             |                 |       |      |               |       |      |     |       |               |        |       |            |         |        |

|                     | DCBA                 | Defects<br>A/B<br>A/C | Agnd<br>An1 | A/Q<br>A//dd      | B/C  | B/gnd         | B/n1<br>B/Q | Bydd            | Cland | C/n1 | C/Q           | C/vdd | D/n1 | D/G | D/vdd | n1/B/gnd      | n1/vdd | urgna | 00044      | Outputs | ø      |

|                     | 0000                 | 000                   |             | 1 0               | 0 0  | 0             | 1 1         | 0 (             | 0 0   | 0    | 1             | 0 0   |      | 1   |       | 1             |        |       | 0 0        |         | Η      |

|                     | 0001                 | 000                   | 00          | 0 0               | 0 0  | 0             | 1 1         | 1 (             | 0 0   |      |               | 0 0   | ) 1  | 1   | 0     | 1             | 0      | 1 (   | 0 0        |         | Η      |

| Impossible to       | 0010                 | 000                   | 01          | 1 1               | 0 0  | 0             | 0 0         | $\rightarrow$   | 0 0   |      | $\rightarrow$ | 0 0   | _    |     | 0     | 1             | 0      | _     | 0 0        |         | Η      |

| generate test       | 0011                 | 0 1 1                 |             | 10                | 1 1  | 1             | 1 1         | $ \rightarrow $ | _     | 0    |               | 0 0   | ) 0  | 0   | 0     | 0             | 1      | 0 (   | D 1        |         | L      |

| -                   | 0100                 |                       | + + +       | 10                | 0 0  | +             | 1 1         |                 | _     | 0    |               | 0 0   |      | +   |       | 1             |        | -     |            |         | H      |

| vectors for         | 0101                 | 000                   |             | 0 0               | 0 0  | $\rightarrow$ | 1 1         |                 | 0 0   |      |               | 0 0   |      | +   |       | 1             | -      | -     |            |         | Η      |

| A/B and D/C         | 0110                 | 0 0 0                 |             | 11                | 0 0  | ++            | 0 0         | $\rightarrow$   | _     |      | $\rightarrow$ | 0 0   |      |     |       | 1             | -      | _     | 0 0        |         | Η      |

| A/D and D/C         | 0111                 | 001                   |             | 10                | 0 1  | ++            | 0 1         |                 | _     | 0    |               | 0 0   | _    |     |       | 0             | -+-    |       | 0 1        |         | L      |

|                     | 1000                 |                       | + + +       | 10                | 0 0  | ++            | 11          | $ \rightarrow $ | _     | 1    |               | 10    | _    |     |       | 1             | -+-    | -     | 0 0        |         | H      |

|                     | 1001                 |                       | + + +       | 0 0               | 0 0  | ++            | 11          |                 |       |      |               | 10    | _    |     |       | 1             | -+-    |       |            |         | H<br>H |

|                     | 1010                 |                       |             | 11                | 0 0  | +             | _           |                 | _     | 1    |               | 10    | _    |     |       | 1             | -+-    | -     |            |         | _      |

|                     | 1011                 | 0 1 0                 |             | <b>1</b> 0<br>0 0 | 10   | ++            | 0 1         |                 | _     | 0    |               | _     | _    |     |       |               |        |       | 0 1<br>1 1 |         | L<br>L |

|                     | 1100<br>1101         | 0 1 1                 |             | 0 0               | 11   | +-+           |             |                 | _     | -    |               | 0 1   |      |     |       | 0<br>0        |        |       | 1 1        |         | L      |

|                     | 1110                 |                       |             | 0 0               | _    | ++            |             |                 |       |      |               |       | _    |     |       | $\rightarrow$ | 0      | _     | 1 1        |         | L      |

|                     | 1111                 |                       |             | 1 0               |      | +             | 01          |                 |       |      |               |       | _    |     |       |               |        |       |            |         | L      |

|                     |                      |                       |             |                   |      |               | -<br>-      |                 |       | Ū    |               | -     |      |     | Ū     | -             | Ť      |       |            |         | -      |

|                     | Coverage             | 0 1 1                 | 11          | 1 1               | 1 1  | . 1           | 1 1         | 1 (             | 0 1   | 1    | 1             | 1 1   | L 1  | 1   | 1     | 1             | 1      | 1 :   | 1 1        | -       |        |

|                     | P                    | -                     |             |                   |      |               |             |                 | K     |      |               |       |      |     |       |               |        |       |            |         |        |

|                     | Coverage: 92.593%    | )                     |             |                   |      |               |             | -               |       |      | ur            | d     | ot   | ρ   | -te   | 20            | lf     | aı    | ılı        | s       |        |

|                     |                      |                       |             |                   |      |               |             |                 |       |      |               |       |      |     |       |               |        |       |            |         |        |

|                     |                      | 🖷 Sav                 | e           |                   |      | A P           | Print.      |                 |       |      |               | Ì     | Clo  | se  |       |               |        |       |            |         |        |

| r Jutman, Warsaw, F |                      |                       |             |                   |      |               |             |                 |       |      |               | _     |      |     |       |               |        |       |            |         |        |

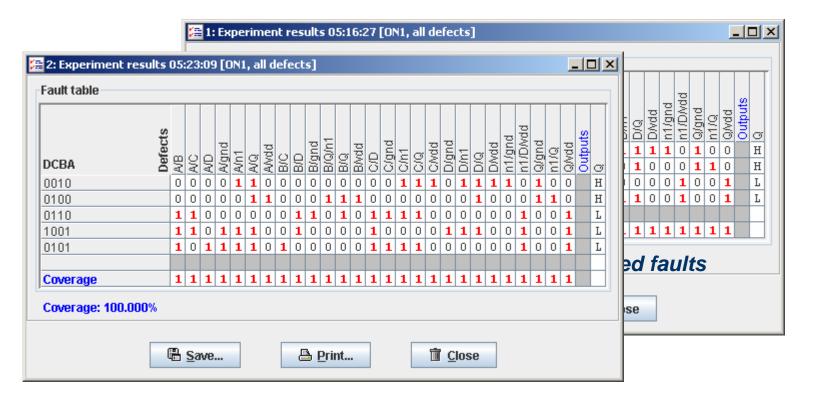

*I*<sub>DDO</sub> versus voltage testing

Show Transistor Level Schematics

|   | SHOW | mansistui | Level | Schem |

|---|------|-----------|-------|-------|

| - |      |           |       |       |

| Simulation Options                    | - |                   |         | _          | _          | _   | _     | _    | _  | _    | _   | _   | _     | _           | _   | _    | _   | _     | _    | _   | _     | _     | _            | _   |        |          |                 |       |                 |       | _        |   |

|---------------------------------------|---|-------------------|---------|------------|------------|-----|-------|------|----|------|-----|-----|-------|-------------|-----|------|-----|-------|------|-----|-------|-------|--------------|-----|--------|----------|-----------------|-------|-----------------|-------|----------|---|

| ○ All defects                         |   | 3: Experiment re  | sults   | ; 0!       | 9:3        | 7:0 | 17 [  | (AN  | 1, | all  | de  | fec | ts,   | ld          | dq  | ac   | tiv | ate   | d]   |     |       |       |              |     |        |          |                 |       | 60 E            | r a   | 7        | X |

| ○ All stuck-at faults                 |   | Fault table       |         |            |            |     |       |      |    |      |     |     |       |             |     |      |     |       |      |     |       |       |              |     |        |          |                 |       |                 |       |          |   |

| Single defect: B/Q                    |   |                   | s       |            |            |     |       |      |    |      |     |     |       |             |     |      |     |       |      |     |       |       |              |     |        | pu       |                 |       |                 |       | <i>"</i> | Ī |

| ✓ Activate I <sub>DDQ</sub>           |   | DCBA              | Defects | AB         | AC         | AD  | Avgnd | A/n1 | AQ | Avdd | B/C | B/D | B/gnd | B/n1        | B/Q | BNdd | Q,O | C/gnd | C/n1 | C/Q | C/vdd | D/gnd | D/n1         | D/O | Divide | n1/B/gnd | n1/vdd          | Q/gnd | n1/Q            | Q/vdd | sindino  | 5 |

| · · · · · · · · · · · · · · · · · · · |   | 1110              |         | 1          | 1          | 1   | õ     | 1    | 0  | 1    | 0   | 0   | 1     | 0           | 1   | 0    |     | 1     | 0    |     | 0     | 1     | 0            |     |        | 1        |                 | 0     | 1               | 1     | I        | - |

| Ready Experime                        |   |                   |         | -          | -          | -   | -     | -    | -  | -    | -   |     | -     | -           | -   | -    |     | _     | _    |     |       |       |              |     |        | -        | $ \rightarrow $ |       | $ \rightarrow $ | ÷     |          | _ |

| P                                     |   | 0011              |         | 0          | 1          | 1   | L     | L    | 1  | 0    | 1   | 1   | 1     | 1           | 1   | 0    | 0   | 0     | 0    |     | 1     | 0     | 0            | 0   | 1      | 1        | 1               | 0     | 0               | -     | I        |   |

|                                       |   | 0101              |         | 1          | 0          | 1   | 1     | 0    | 0  | 0    | 1   | 0   | 0     | 1           | 1   | 1    | 1   | 1     | 0    | 0   | 0     | 0     | 1            | 1   | 1      | 1        | 0               | 1     | 0               | 0     | E        |   |

|                                       |   | 1010              |         | 1          | 0          | 1   | 0     | 1    | 1  | 1    | 1   | 0   | 1     | 0           | 0   | 0    | 1   | 0     | 1    | 1   | 1     | 1     | 0            | 0   | 0      | 1        | 0               | 1     | 0               | 0     | H        | 1 |

|                                       |   |                   |         |            |            |     |       |      |    |      |     |     |       |             |     |      |     |       |      |     |       |       |              |     |        |          |                 |       |                 |       |          | 1 |

|                                       |   | Coverage          |         | 1          | 1          | 1   | 1     | 1    | 1  | 1    | 1   | 1   | 1     | 1           | 1   | 1    | 1   | 1     | 1    | 1   | 1     | 1     | 1            | 1   | 1      | 1        | 1               | 1     | 1               | 1     |          | 1 |

|                                       |   |                   | _       |            |            |     |       |      |    |      |     |     |       |             |     | _    |     |       |      |     |       |       | _            | _   |        |          |                 |       |                 |       | _        | 1 |

| I <sub>DDQ</sub> testing              | S | olves t           | h       |            | (          | 2   | h     | S    | E  | Y    |     | 12  | al    | h           | il  | H    | ٢١  |       | r    |     | "(    | כ     | h            |     | A      | n        | 1               |       |                 |       |          |   |

| DDQ COOLING                           |   |                   |         |            |            |     |       |      |    |      |     |     |       |             |     |      | -)  |       | r    |     |       |       |              | -   | -      | •••      | •               |       |                 |       |          |   |

|                                       |   | Coverage: 100.000 | 1%      |            |            |     |       |      |    |      |     |     |       |             |     |      |     |       |      |     |       |       |              |     |        |          |                 |       |                 |       |          |   |

|                                       |   |                   |         |            |            |     |       |      |    |      |     |     |       |             |     |      |     |       |      |     |       |       |              |     |        |          |                 |       |                 |       |          |   |

|                                       |   |                   | 6       | <u>n</u>   | <u>S</u> a | ~~~ | _     |      |    |      |     |     | λ. ε  | <u>Prir</u> | nt  | _    |     |       |      |     | 南     |       | <u>;</u>  0: | 20  |        |          |                 |       |                 |       |          |   |

|                                       |   |                   |         | <b>(</b> ) | 30         | vC. |       |      |    |      |     |     | 9 5   | _           | R   | •    |     |       |      |     |       | 9     | 2103         | 56  |        |          |                 |       |                 |       |          |   |

|                                       |   |                   | _       | -          | _          | _   | _     | _    | _  | _    | _   | _   | _     | _           | _   | _    | -   | _     | _    | _   | -     | -     | _            | _   | _      | _        | _               | _     | _               | _     | _        | _ |

#### Memory effects due to shorts

#### Memory effects due to shorts

| ment results 11:3 | 0:37 [CB1, single            | defect: I1/ 💶 🗆 🗙                                |

|-------------------|------------------------------|--------------------------------------------------|

| ts                |                              |                                                  |

| ¥2                | ¥1                           | PASS/FAIL                                        |

| 1/Fail            | 1/0K                         | FAIL                                             |

| 0/ок              | 0/ок                         | PASS                                             |

| 0/0K              | 0/Fail                       | FAIL                                             |

|                   |                              |                                                  |

|                   |                              |                                                  |

|                   |                              |                                                  |

|                   |                              |                                                  |

| we                | 🖴 Print                      | <u> C</u> lose                                   |

|                   | ts<br>1/Fail<br>0/0K<br>0/0K | Y2 Y1<br>1/Fail 1/OK<br>0/OK 0/OK<br>0/OK 0/Fail |

#### Memory effects due to opens

| ✓ DefSim by Testonica File Options Window Help |   |                   |

|------------------------------------------------|---|-------------------|

| NA2_o: NAND( A, B ) - opens                    |   | Input Vectors [4] |

| MAZ_0. MAND(A, D) - Opens                      |   | BA                |

| Gate-Level Schematics                          |   | 00                |

|                                                |   | 10<br>11          |

| nand2 0                                        |   | 10                |

|                                                |   |                   |

| Show Transistor Level Schematics               |   |                   |

| Measurement Options                            |   | 📾 Open 🖷 Save     |

| ○ All defects                                  |   | Generate          |

| All stuck at faults                            |   | SAF ATPG          |

| Single defect: NA2_08                          | n | Exhaustive Test   |

| Activate I <sub>DDQ</sub>                      |   | Random Test 5     |

| Ready Experiment finished sucessfully          | 1 | p                 |

11 10

<u>BA</u>

00

10

#### Memory effects due to opens

| BA         | Q          | PASS/FAIL |                |

|------------|------------|-----------|----------------|

| 00         | 1/0K       | PASS      |                |

| 10         | 1/0K       | PASS      |                |

| 11         | 0/0K       | PASS      |                |

| 10         | 0/Fail     | FAIL      |                |

|            |            |           |                |

| <b>B</b> 9 | <u>ave</u> | 🕒 Print   | <u> C</u> lose |

## Future work

#### Current version is only the first step; our plans are

X

- Looking into *other* defect types increasing diversity

- Implementing *didactically* interesting defects

- Development of new DefSim IC versions for research needs

- Updating DefSim IC using upcoming CMOS technologies

- Development of new teaching lab scenarios

# Conclusions

- The educational integrated circuit *DefSim* was designed and manufactured.

- This chip is dedicated to development of students' skills in fault simulation and test pattern generation for digital circuits.

M

- It allows applying both voltage (i.e. logical) and current test methods and offers comparing of their efficiencies on basic digital circuit examples.

- Operation of DefSim was verified experimentally.

- "Plug and Play" DefSim bundle represents a unique and easy to handle educational and research environment.

## Thank your for your attention!

Try DefSim at http://www.defsim.com

Read more about DefSim at www.testonica.com

Read more about REASON project at http://reason.imio.pw.edu.pl/